DocID024597 Rev 5 873/1830

RM0351 Hash processor (HASH)

875

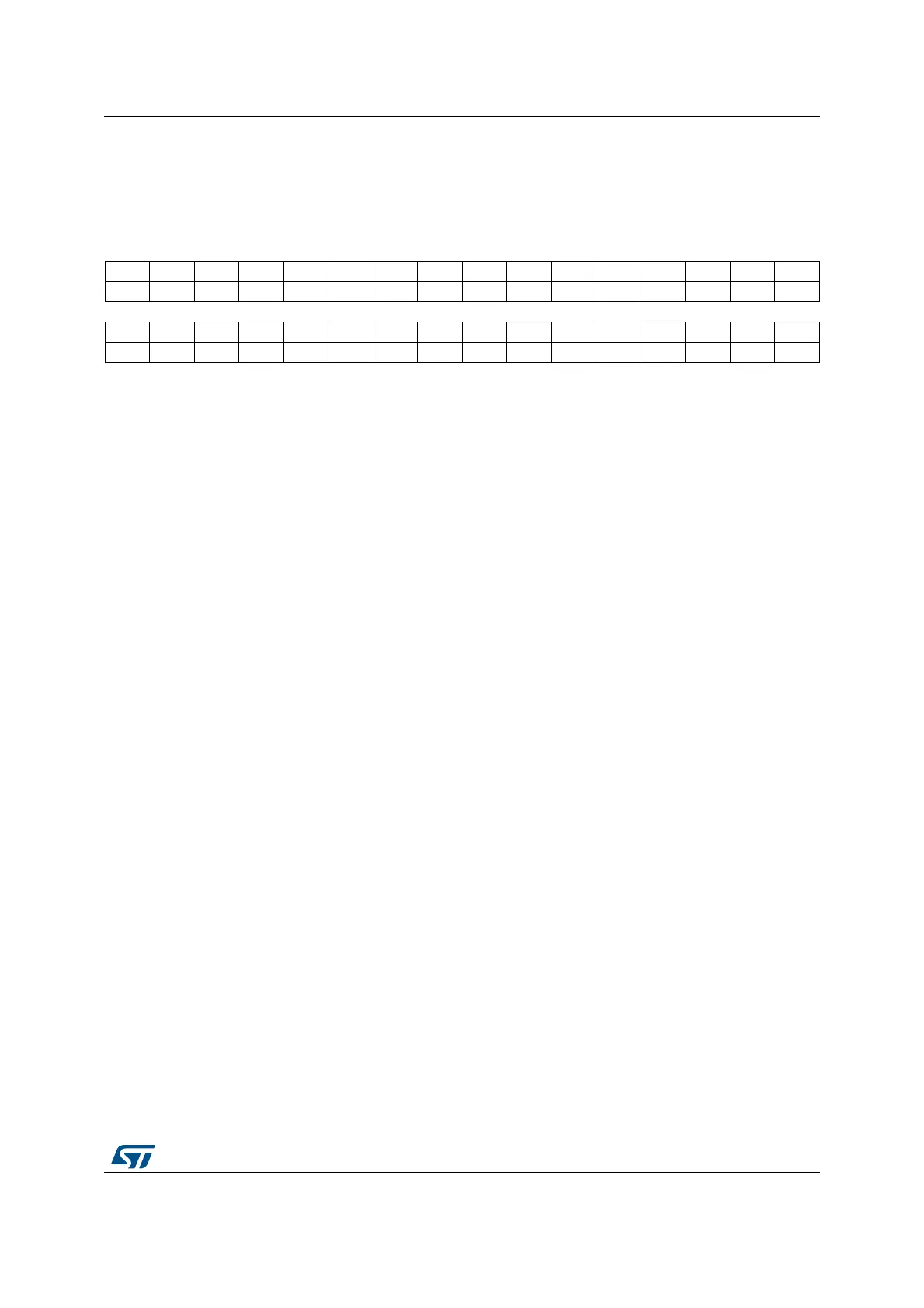

29.6.6 HASH status register (HASH_SR)

Address offset: 0x24

Reset value: 0x0000 0001

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

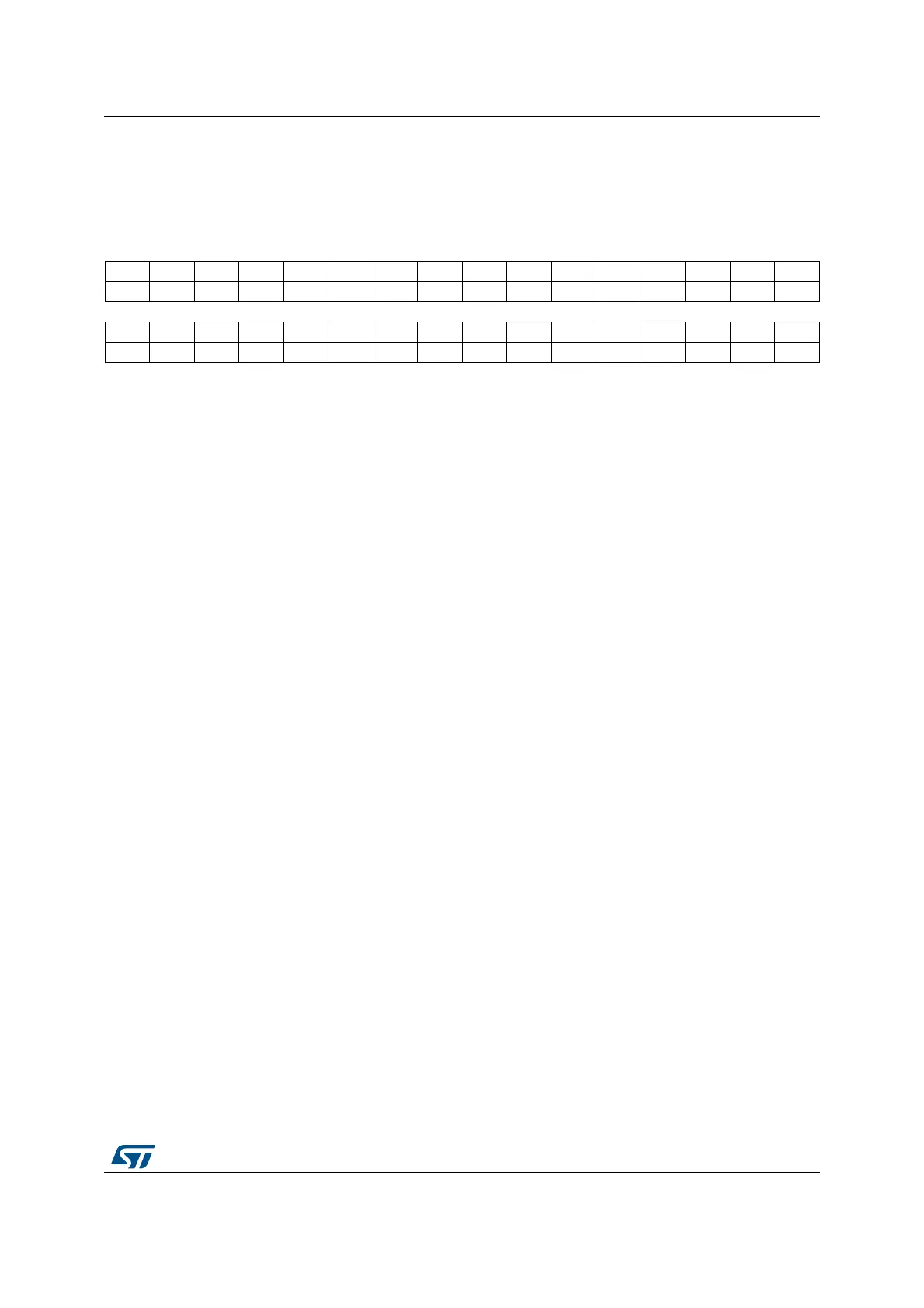

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. BUSY DMAS DCIS DINIS

rrrc_w0rc_w0

Bits 31:4 Reserved, must be kept at reset value

Bit 3 BUSY: Busy bit

0: No block is currently being processed

1: The hash core is processing a block of data

Bit 2 DMAS: DMA Status

This bit provides information on the DMA interface activity. It is set with DMAE

and cleared when DMAE=0 and no DMA transfer is ongoing. No interrupt is

associated with this bit.

0: DMA interface is disabled (DMAE=0) and no transfer is ongoing

1: DMA interface is enabled (DMAE=1) or a transfer is ongoing

Bit 1 DCIS: Digest calculation completion interrupt status

This bit is set by hardware when a digest becomes ready (the whole message

has been processed). It is cleared by writing it to 0 or by writing the INIT bit to 1

in the HASH_CR register.

0: No digest available in the HASH_Hx registers

1: Digest calculation complete, a digest is available in the HASH_Hx registers.

An interrupt is generated if the DCIE bit is set in the HASH_IMR register.

Bit 0 DINIS: Data input interrupt status

This bit is set by hardware when the input buffer is ready to get a new block (16

locations are free). It is cleared by writing it to 0 or by writing the HASH_DIN

register.

0: Less than 16 locations are free in the input buffer

1: A new block can be entered into the input buffer. An interrupt is generated if

the DINIE bit is set in the HASH_IMR register.

Loading...

Loading...