RM0008 General-purpose and alternate-function I/Os (GPIOs and AFIOs)

111/690

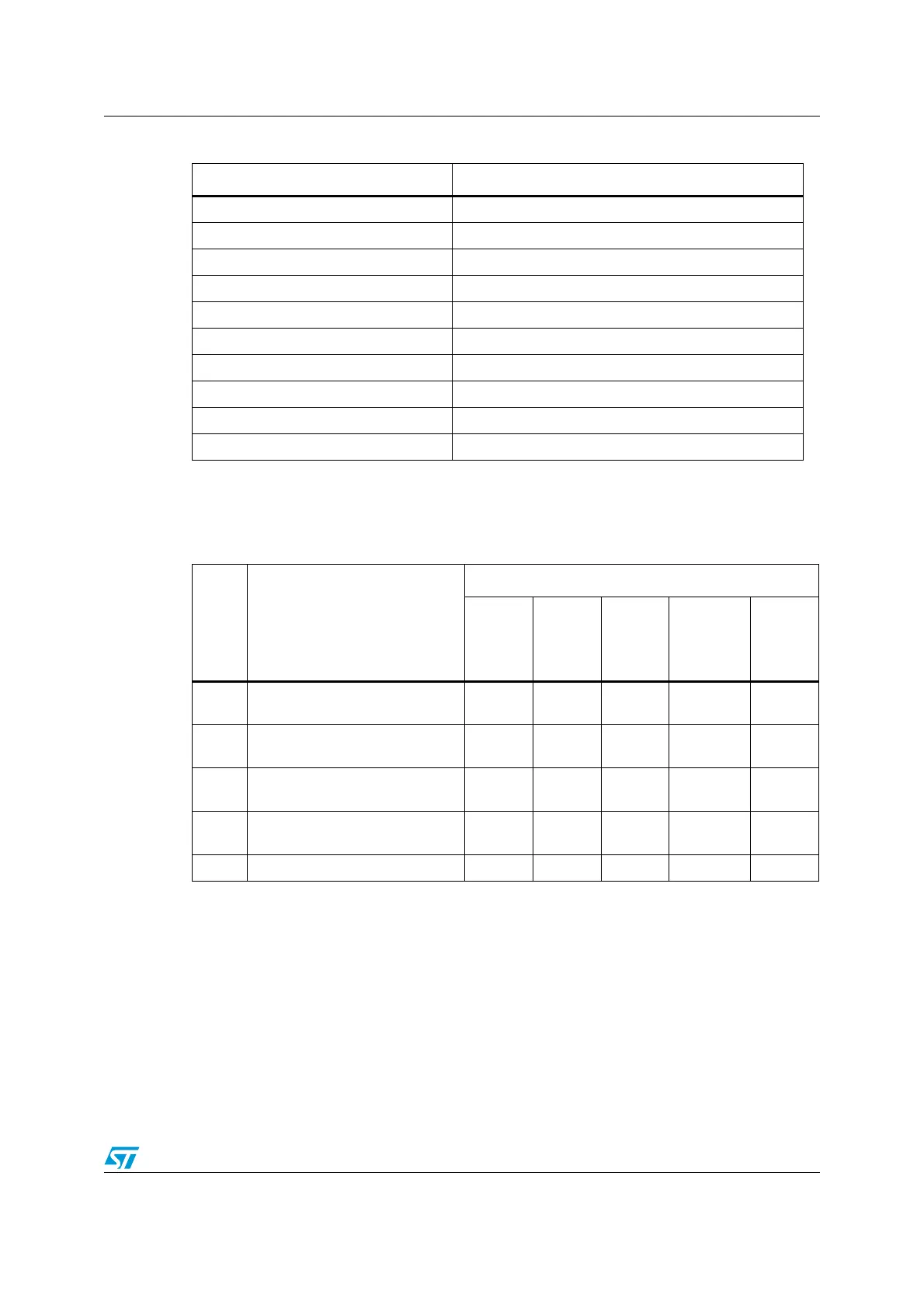

To optimize the number of free GPIOs during debugging, this mapping can be configured in

different ways by programming the SWJ_CFG[1:0] bits in the AF remap and debug I/O

configuration register (AFIO_MAPR). Refer to Tabl e 1 9

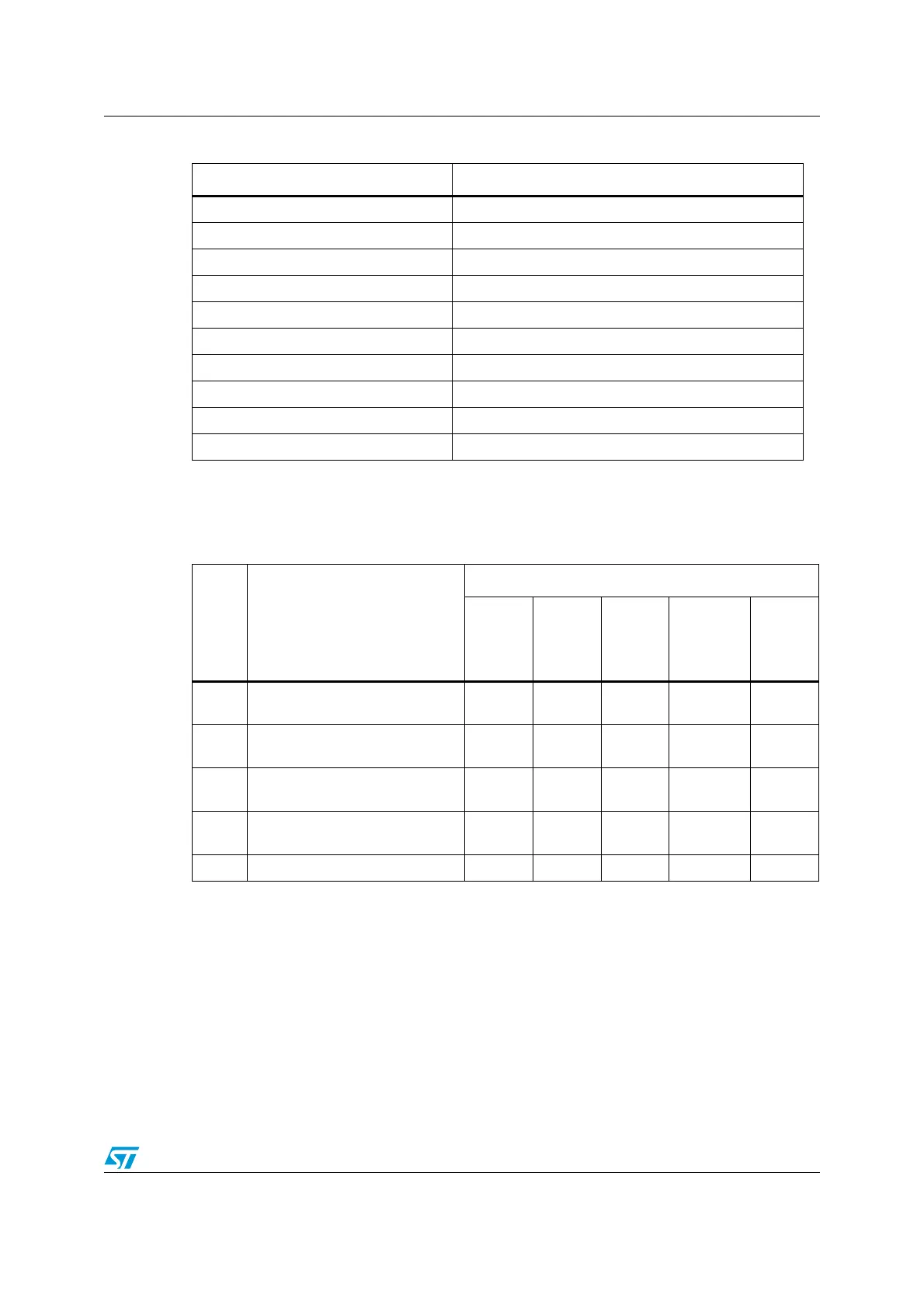

Table 18. Debug interface signals

Alternate function GPIO port

JTMS / SWDIO PA13

JTCK / SWCLK PA14

JTDI PA15

JTDO / TRACESWO PB3

JNTRST PB4

TRACECK PE2

TRACED0 PE3

TRACED1 PE4

TRACED2 PE5

TRACED3 PE6

Table 19. Debug port mapping

SWJ

_CFG

[2:0]

Available debug ports

SWJ I/O pin assigned

PA.13 /

JTMS/

SWDIO

PA. 14 /

JTCK/S

WCLK

PA.15 /

JTDI

PB.3 /

JTDO/

TRACE

SWO

PB.4/

JNTRST

000

Full SWJ (JTAG-DP + SW-DP)

(Reset state)

XXX X X

001

Full SWJ (JTAG-DP + SW-DP)

but without JNTRST

XXX xfree

010

JTAG-DP Disabled and

SW-DP Enabled

X X free free

(1)

1. Released only if not using asynchronous trace.

free

100

JTAG-DP Disabled and

SW-DP Disabled

free free free free free

Other Forbidden

Loading...

Loading...