General-purpose timer (TIMx) RM0008

284/690

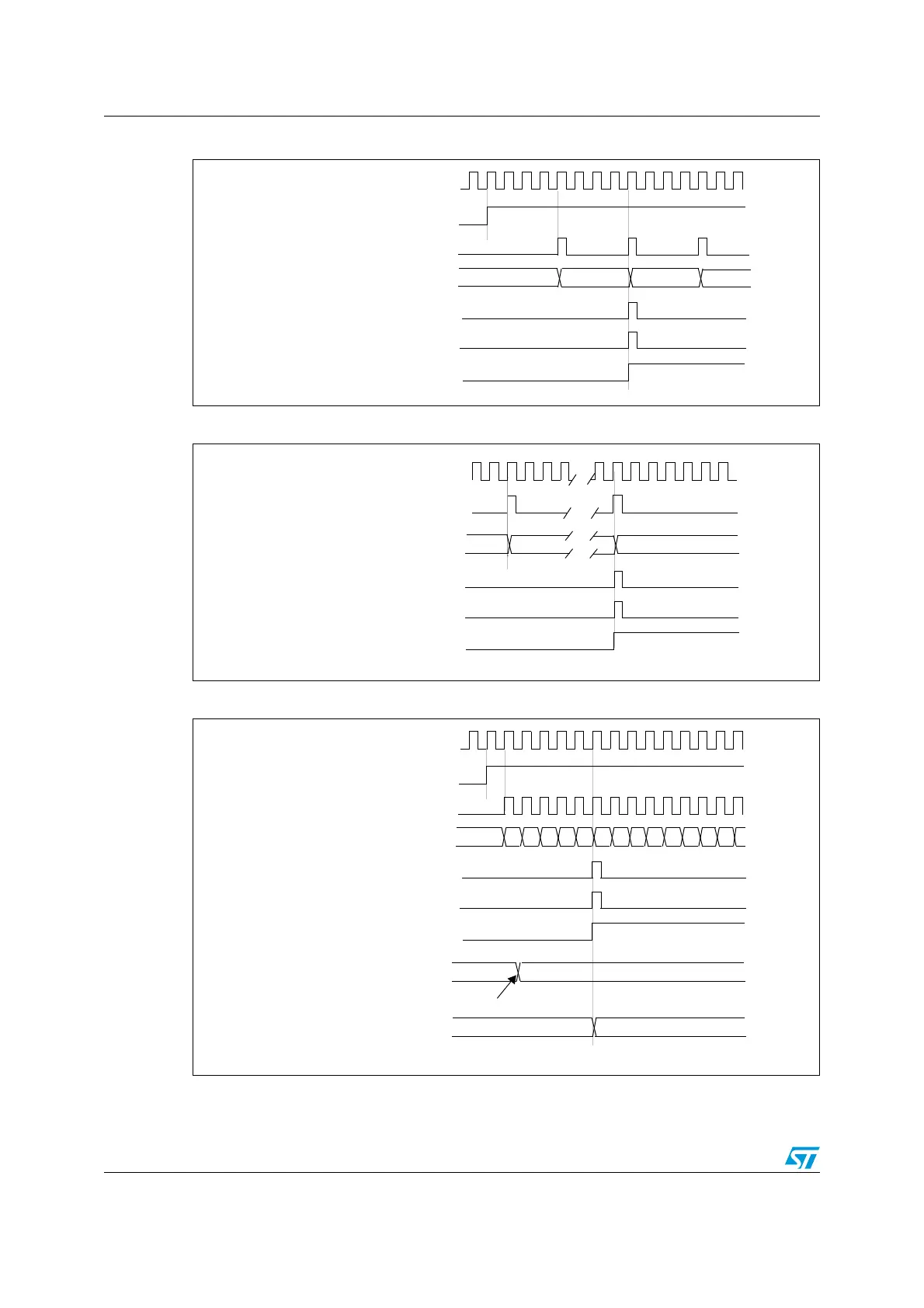

Figure 111. Counter timing diagram, internal clock divided by 4, TIMx_ARR=0x36

Figure 112. Counter timing diagram, internal clock divided by N

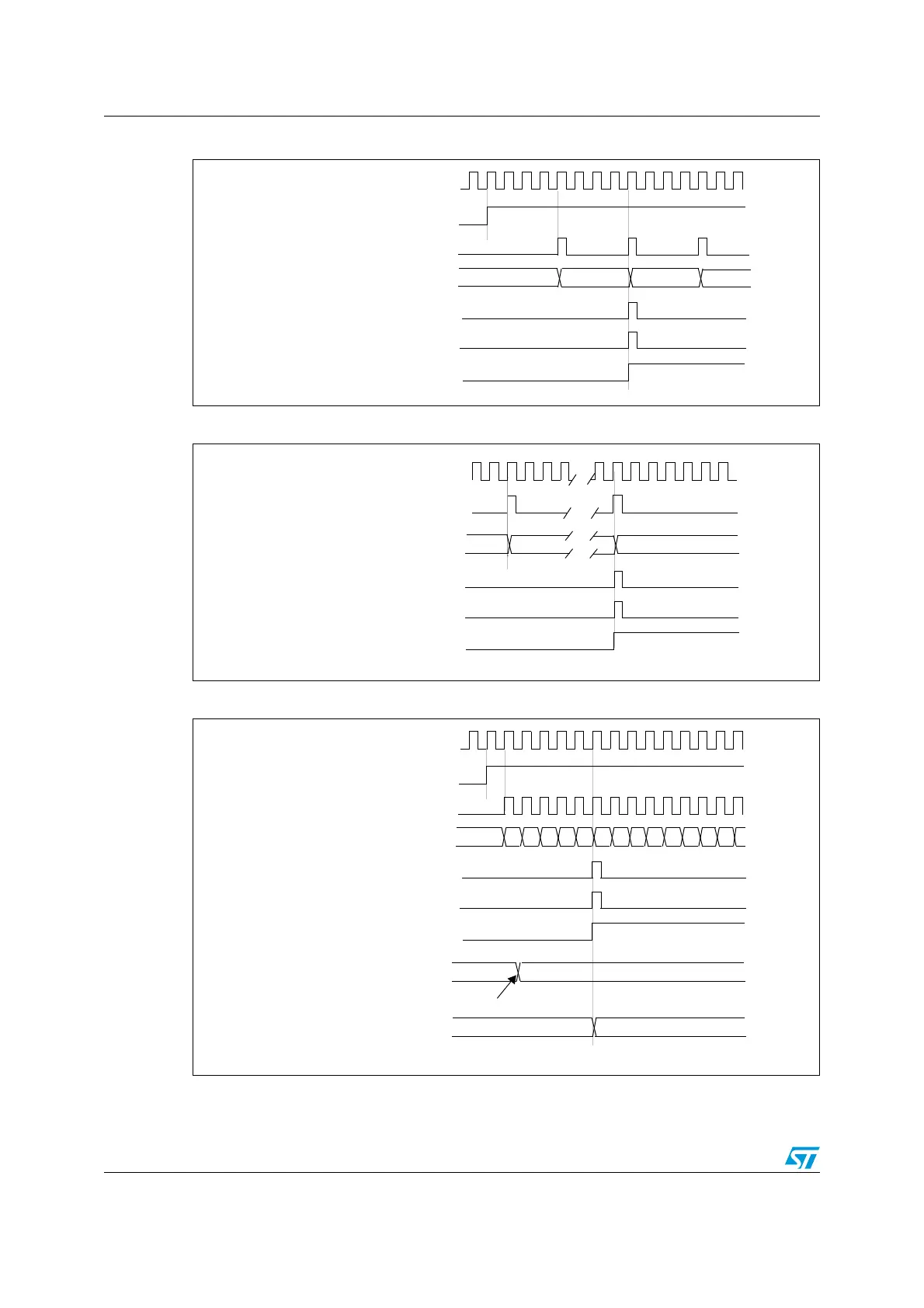

Figure 113. Counter timing diagram, Update event with ARPE=1 (counter underflow)

CK_INT

0036 0035

CNT_EN

Timer clock = CK_CNT

Counter register

Update interrupt flag (UIF)

0034

0035

Counter overflow (cnt_ovf)

Update event (UEV)

Note: Here, center-aligned mode 2 or 3 is used with an UIF on overflow

Timer clock = CK_CNT

Counter register

00

20

1F

Update interrupt flag (UIF)

Counter underflow

Update event (UEV)

CK_INT

01

00

CNT_EN

Timer clock = CK_CNT

Counter register

Update interrupt flag (UIF)

Counter underflow

Update event (UEV)

01 02 03 04 05 06 0705 04 03 02 0106

Auto-reload preload register

FD 36

Write a new value in TIMx_ARR

Auto-reload active register

FD 36

CK_INT

Loading...

Loading...