Debug support (DBG) RM0008

654/690

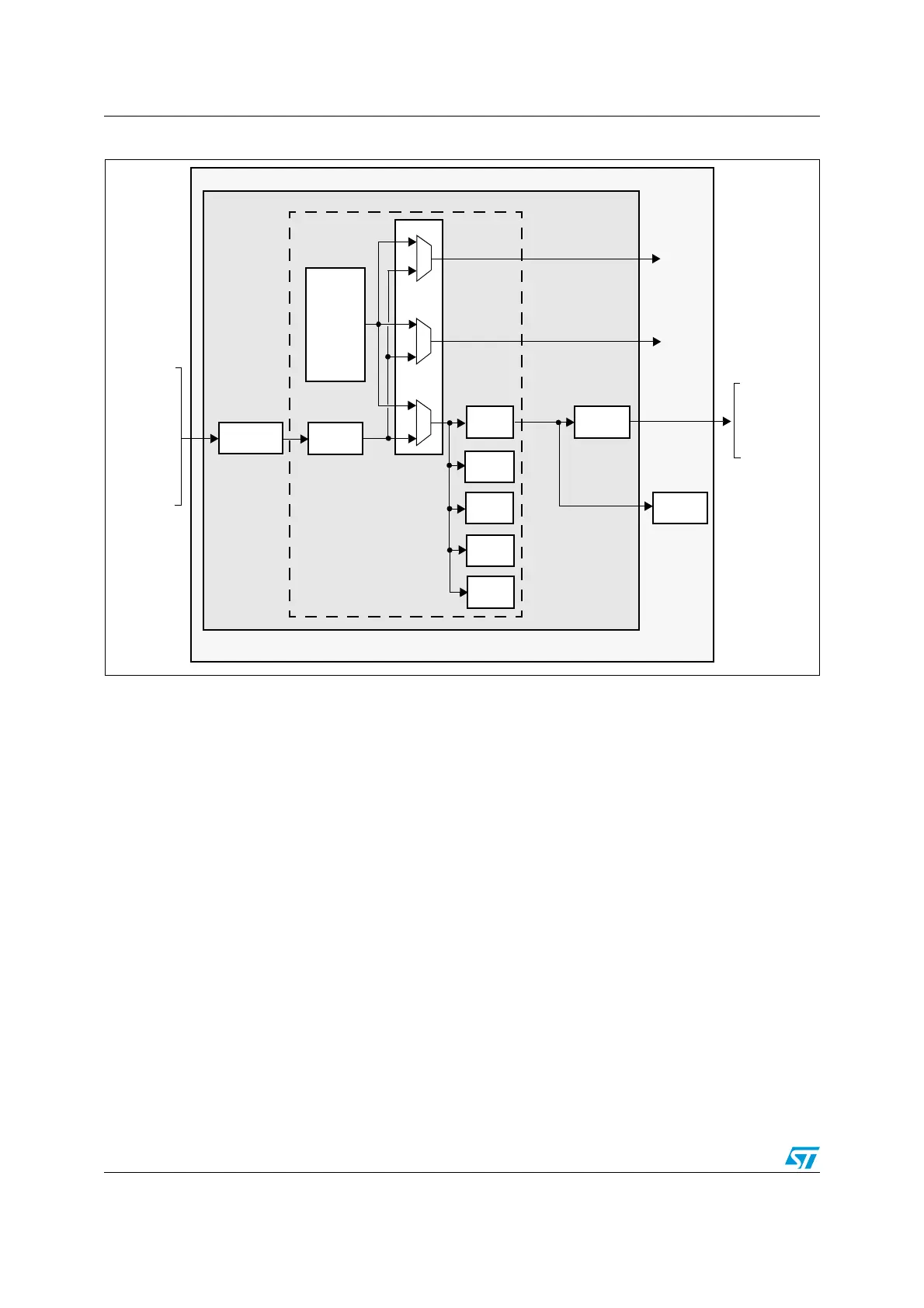

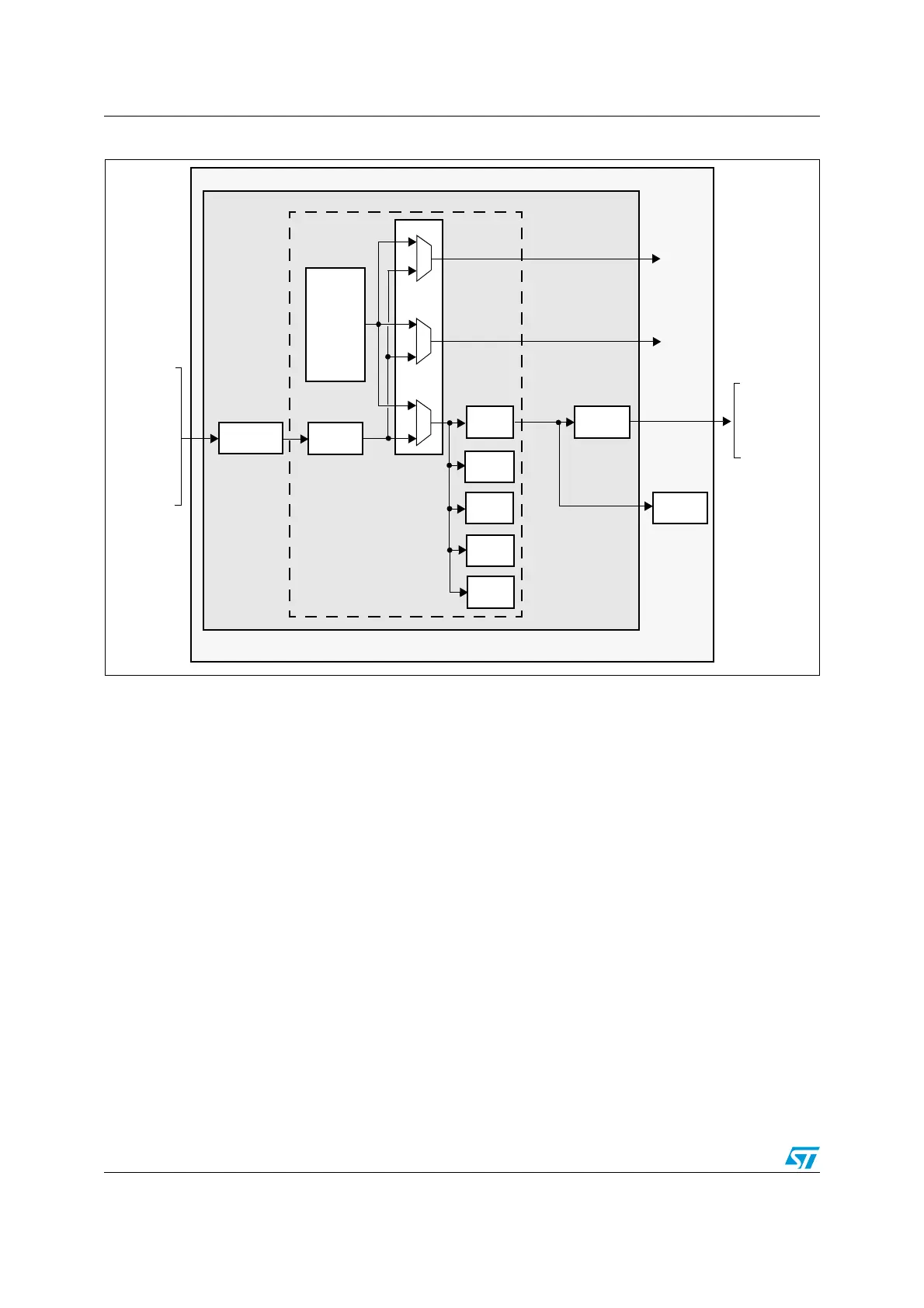

Figure 258. Block diagram of STM32F10xxx-level and Cortex-M3-level debug support

Note: The debug features embedded in the Cortex-M3 core are a subset of the ARM CoreSight

Design Kit.

The ARM Cortex-M3 core provides integrated on-chip debug support. It is comprised of:

● SWJ-DP: Serial wire / JTAG debug port

● AHP-AP: AHB access port

● ITM: Instrumentation trace macrocell

● FPB: Flash patch breakpoint

● DWT: Data watchpoint trigger

● TPUI: Trace port unit interface (available on larger packages, where the corresponding

pins are mapped)

It also includes debug features dedicated to STM32F10xxx:

● Flexible debug pinout assignment

● MCU debug box (support for low-power modes, control over peripheral clocks, etc.)

Note: For further information on debug functionality supported by the ARM Cortex-M3 core, refer

to the Cortex-M3 r1p1 Technical Reference Manual (TRM) and to the CoreSight Design Kit

r1p0 TRM.

Cortex-M3

Core

SWJ-DP

AHB-AP

Bridge

NVIC

DWT

FPB

ITM

TPIU

DCode

interface

System

interface

Internal Private

Peripheral Bus (PPB)

External Private

Peripheral Bus (PPB)

Bus Matrix

Data

Trace Port

DBGMCU

STM32F10x debug support

Cortex-M3 debug support

JTMS/

JTDI

JTDO/

JNTRST

JTCK/

SWDIO

SWCLK

TRACESWO

TRACESWO

TRACECK

TRACED[3:0]

Loading...

Loading...