RM0008 Analog-to-digital converter (ADC)

159/690

The software source trigger events can be generated by setting a bit in a register

(SWSTART and JSWSTART in ADC_CR2).

A regular group conversion can be interrupted by an injected trigger.

10.8 DMA request

Since converted regular channels value are stored in a unique data register, it is necessary

to use DMA for conversion of more than one regular channel. This avoids the loss of data

already stored in the ADC_DR register.

Only the end of conversion of a regular channel generates a DMA request, which allows the

transfer of its converted data from the ADC_DR register to the destination location selected

by the user.

Note: Only ADC1 and ADC3 have this DMA capability. ADC2-converted data can be transferred in

dual ADC mode using DMA thanks to master ADC1.

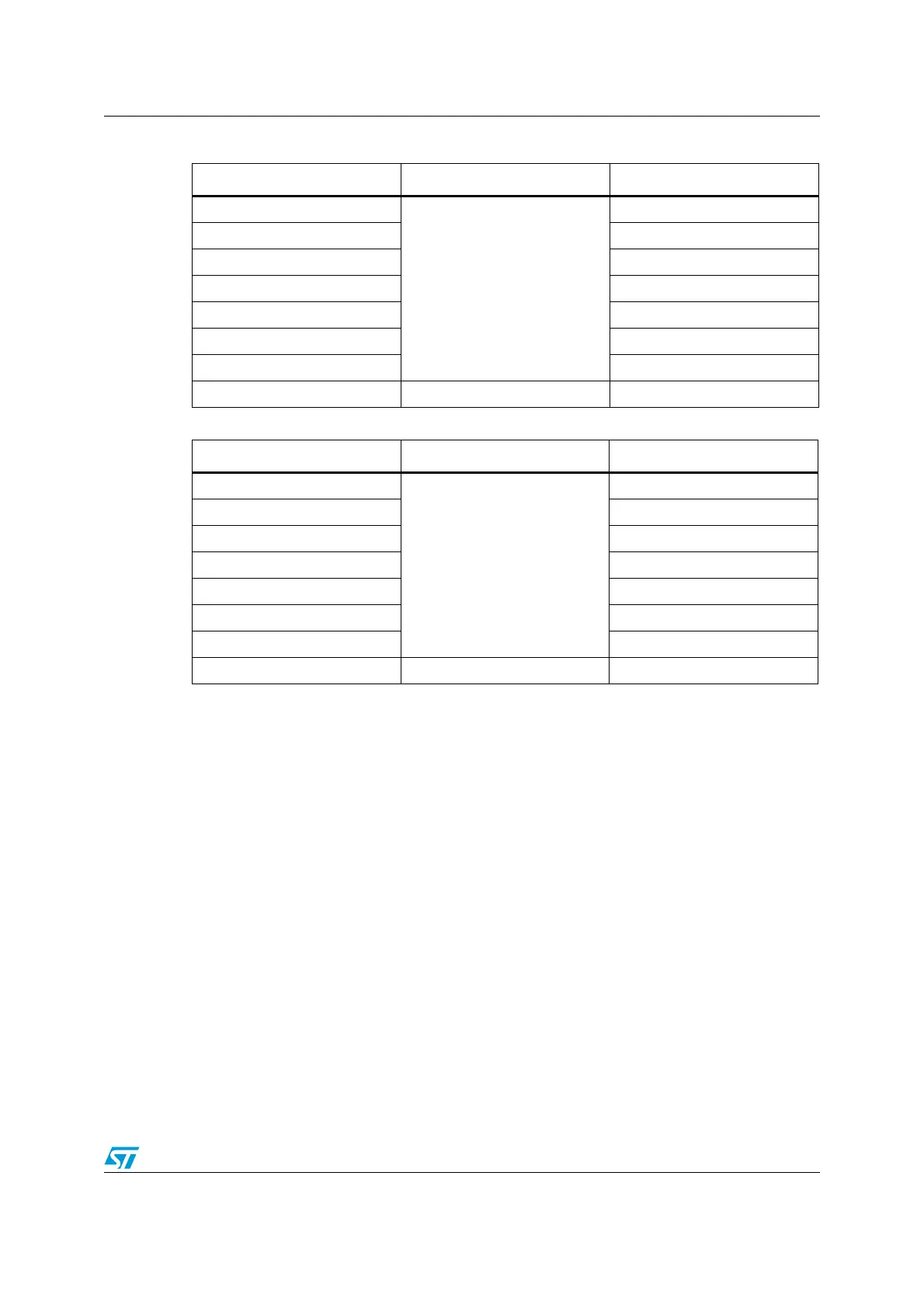

Table 46. External trigger for regular channels for ADC3

Source Connection type EXTSEL[2:0]

TIM3_CC1 event

Internal signal from on-chip

timers

000

TIM2_CC3 event 001

TIM1_CC3 event 010

TIM8_CC1 event 011

TIM8_TRGO event 100

TIM5_CC1 event 101

TIM5_CC3 event 110

SWSTART Software control bit 111

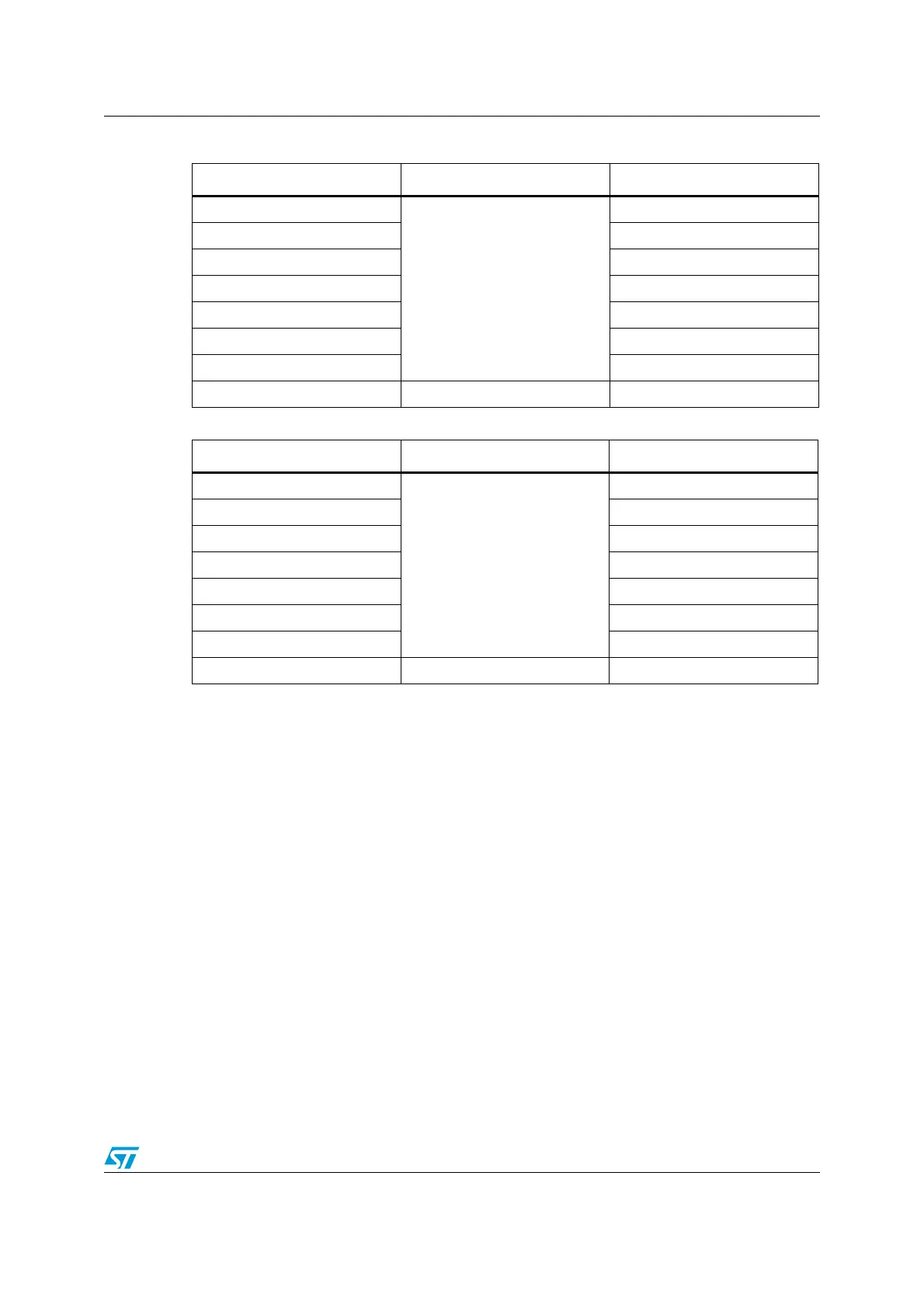

Table 47. External trigger for injected channels for ADC3

Source Connection type JEXTSEL[2:0]

TIM1_TRGO event

Internal signal from on-chip

timers

000

TIM1_CC4 event 001

TIM4_CC3 event 010

TIM8_CC2 event 011

TIM8_CC4 event 100

TIM5_TRGO event 101

TIM5_CC4 event 110

JSWSTART Software control bit 111

Loading...

Loading...