RM0008 DMA controller (DMA)

141/690

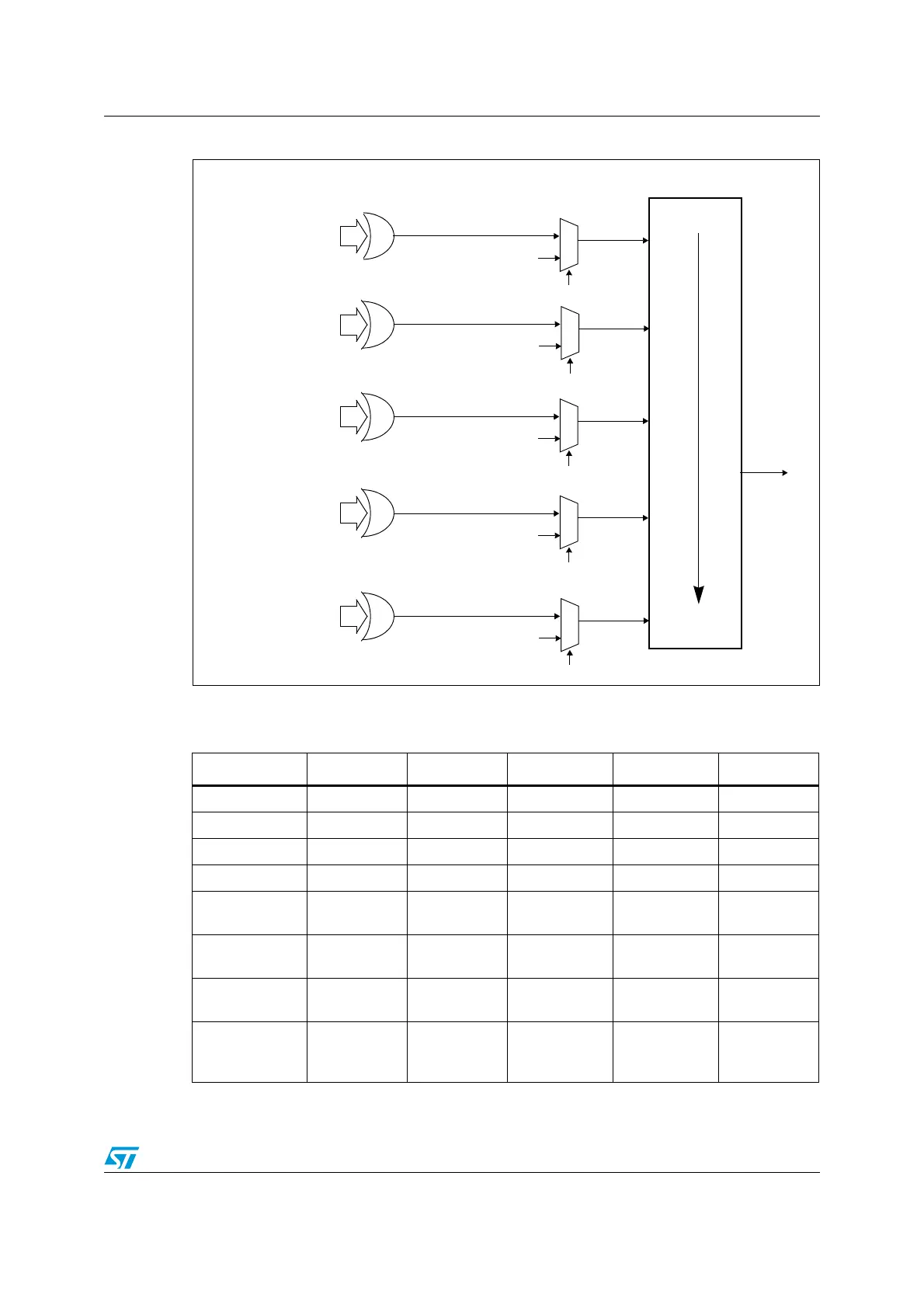

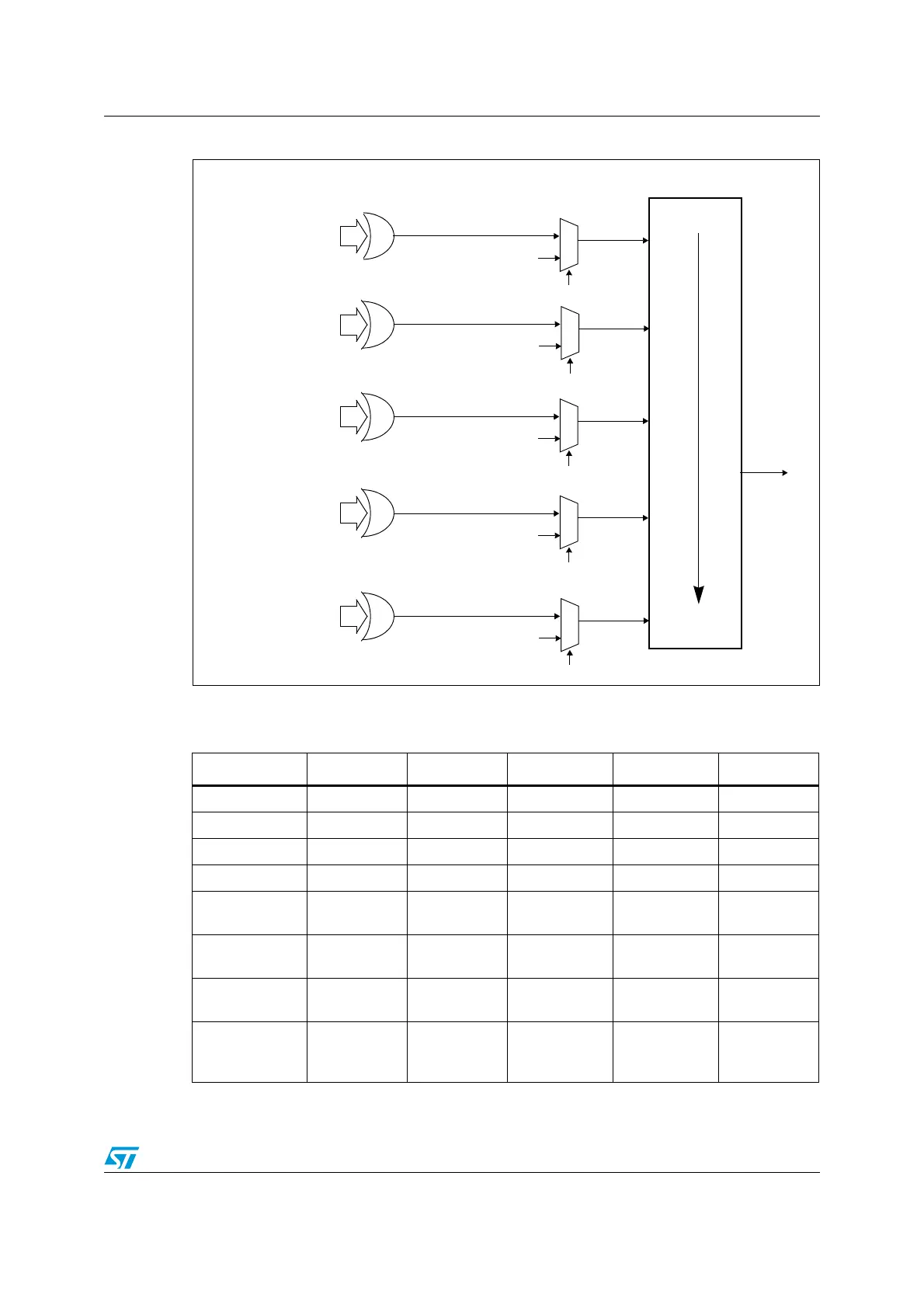

Figure 20. DMA2 request mapping

Tabl e 4 0 lists the DMA2 requests for each channel.

Table 40. Summary of DMA2 requests for each channel

Peripherals Channel 1 Channel 2 Channel 3 Channel 4 Channel 5

ADC3 ADC3

SPI/I2S3 SPI/I2S3_RX SPI/I2S3_TX

UART4 UART4_RX UART4_TX

SDIO SDIO

TIM5

TIM5_CH4

TIM5_TRIG

TIM5_CH3

TIM5_UP

TIM5_CH2 TIM5_CH1

TIM6/

DAC_Channel1

TIM6_UP/

DAC_Channel1

TIM7/

DAC_Channel2

TIM7_UP/

DAC_Channel2

TIM8

TIM8_CH3

TIM8_UP

TIM8_CH4

TIM8_TRIG

TIM8_COM

TIM8_CH1 TIM8_CH2

Fixed hardware priority

Channel 3

internal

HW request 3

HIGH PRIORITY

LOW PRIORITY

Peripheral request signals

Channel 2

HW request 2

Channel 1

SW trigger (MEM2MEM bit)

Channel 1 EN bit

HW request 1

Channel 4

HW request 4

DMA2

Channel 5

HW request 5

request

TIM5_CH2

SDIO

TIM5_CH4

TIM8_UP

TIM7_UP/DAC_Channel2

TIM8_CH3

TIM5_TRIG

Channel 2 EN bit

Channel 3 EN bit

Channel 4 EN bit

Channel 5 EN bit

SW trigger (MEM2MEM bit)

SW trigger (MEM2MEM bit)

SW trigger (MEM2MEM bit)

SW trigger (MEM2MEM bit)

SPI/I2S3_RX

TIM8_CH4

TIM5_UP

TIM5_CH3

TIM8_TRIG

TIM8_COM

SPI/I2S3_TX

TIM8_CH1

UART4_RX

TIM6_UP/DAC_Channel1

ADC3

UART4_TX

TIM8_CH2

TIM5_CH1

Loading...

Loading...