SDIO interface (SDIO) RM0008

466/690

19.9.15 SDIO Data FIFO Register (SDIO_FIFO)

Address offset: 0x80

Reset value: 0x0000 0000

The receive and transmit FIFOs can be read or written as 32-bit wide registers. The FIFOs

contain 32 entries on 32 sequential addresses. This allows the CPU to use its load and store

multiple operands to read from/write to the FIFO.

19.9.16 SDIO Register map

The following table summarizes the SDIO registers.

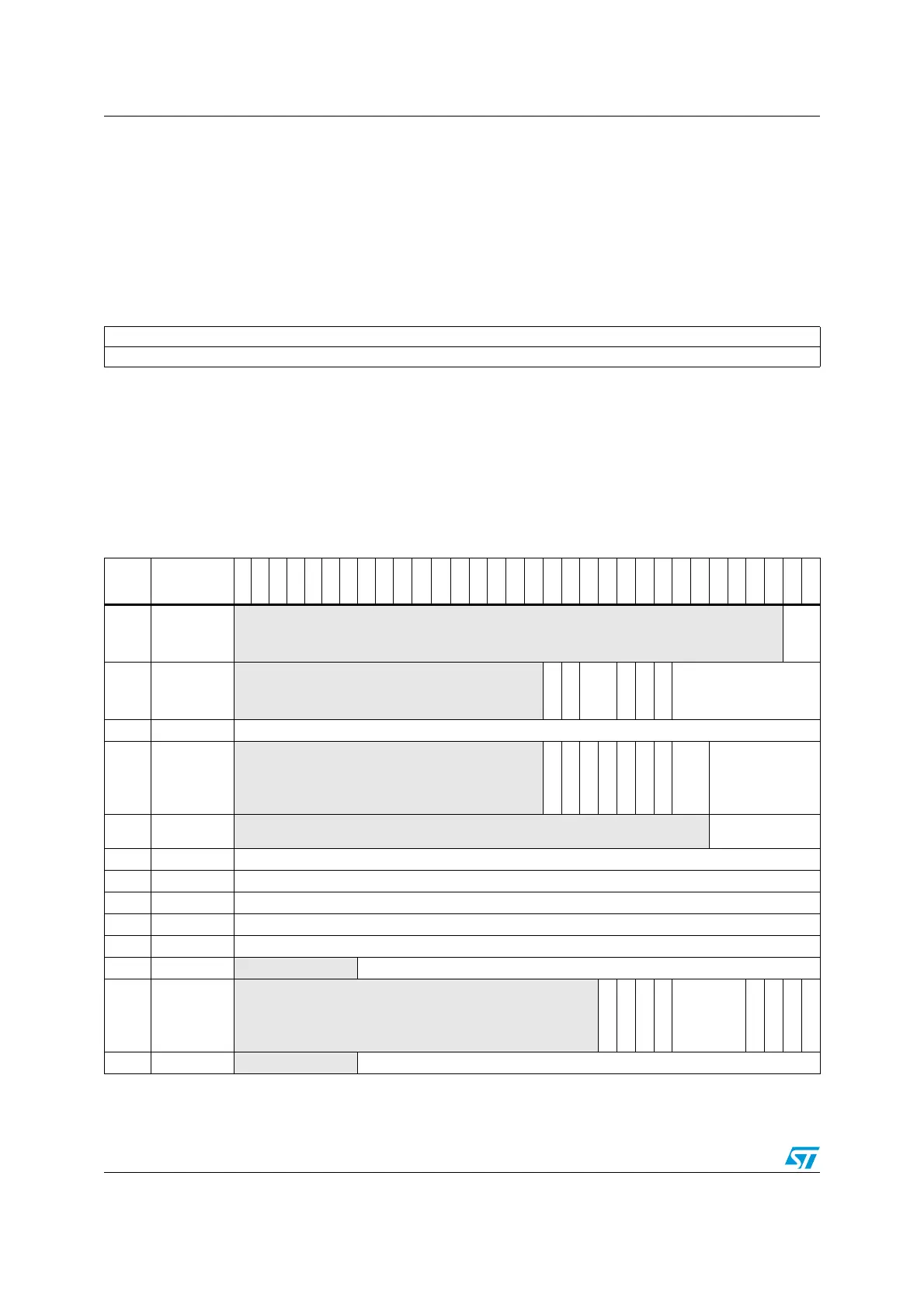

313029282726252423222120191817161514131211109876543210

FIF0Data

r/w

bits 31:0 FIFOData: Receive and transmit FIFO data.

The FIFO data occupies 32 entries of 32-bit words, from address:

SDIO base + 0x080 to SDIO base + 0xFC.

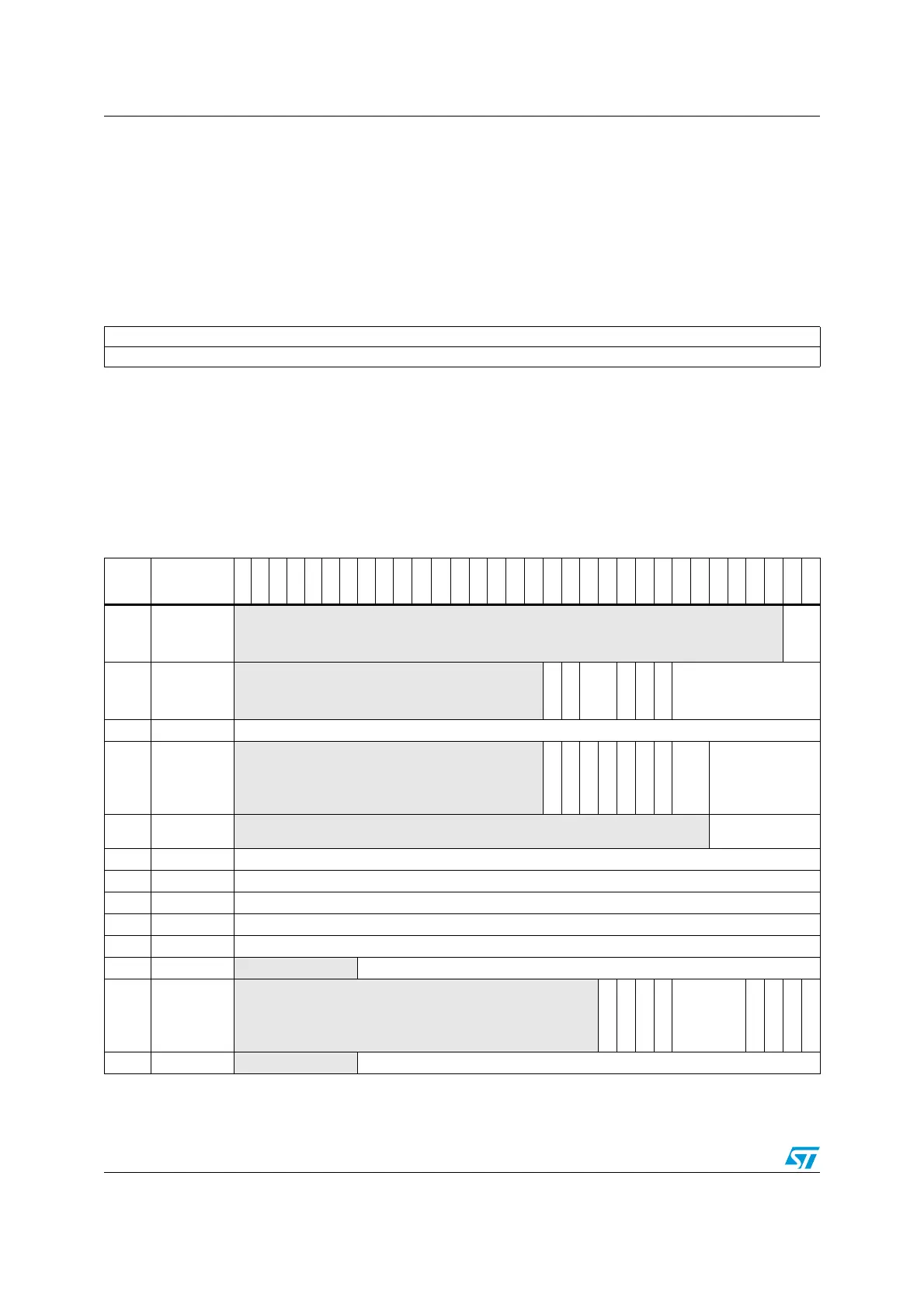

Table 132. SDIO Register map

Ad-

dress

offset

Name 313029282726252423222123191817161514131211109876543210

0x00 SDIO_POWER

Reserved

PWRCTRL

0x04 SDIO_CLKCR

Reserved

HWFC_EN

NEGEDGE

WIDBUS

BYPASS

PWRSAV

CLKEN

CLKDIV

0x08 SDIO_ARG CMDARG

0x0C SDIO_CMD

Reserved

CE-ATACMD

nIEN

ENCMDcompl

SDIOSuspend

CPSMEN

WAITPEND

WAITINT

WAITRESP

CMDINDEX

0x10

SDIO_RESPCM

D

Reserved RESPCMD

0x14 SDIO_RESP1 CARDSTATUS1

0x18 SDIO_RESP2 CARDSTATUS2

0x1C SDIO_RESP3 CARDSTATUS3

0x20 SDIO_RESP4 CARDSTATUS4

0x24 SDIO_DTIMER DATATIME

0x28 SDIO_DLEN

Reserved DATALENGTH

0x2C SDIO_DCTRL

Reserved

SDIOEN

RWMOD

RWSTOP

RWSTART

DBLOCKSIZE

DMAEN

DTMODE

DTDIR

DTEN

0x30 SDIO_DCOUNT Reserved DATACOUNT

Loading...

Loading...