General-purpose timer (TIMx) RM0008

322/690

13.4.8 Capture/compare mode register 2 (TIMx_CCMR2)

Address offset: 0x1C

Reset value: 0x0000

Refer to the above CCMR1 register description.

Output Compare mode

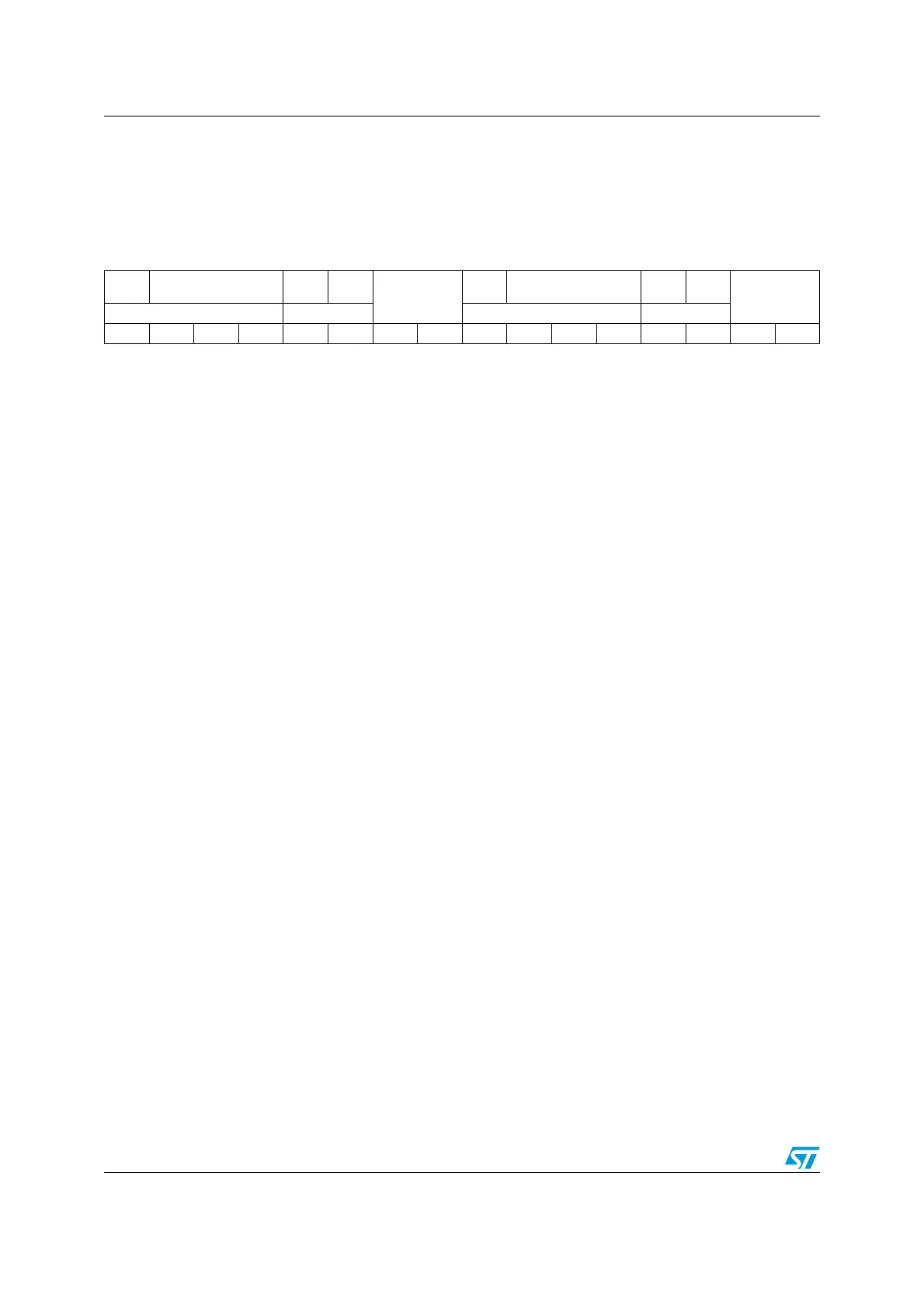

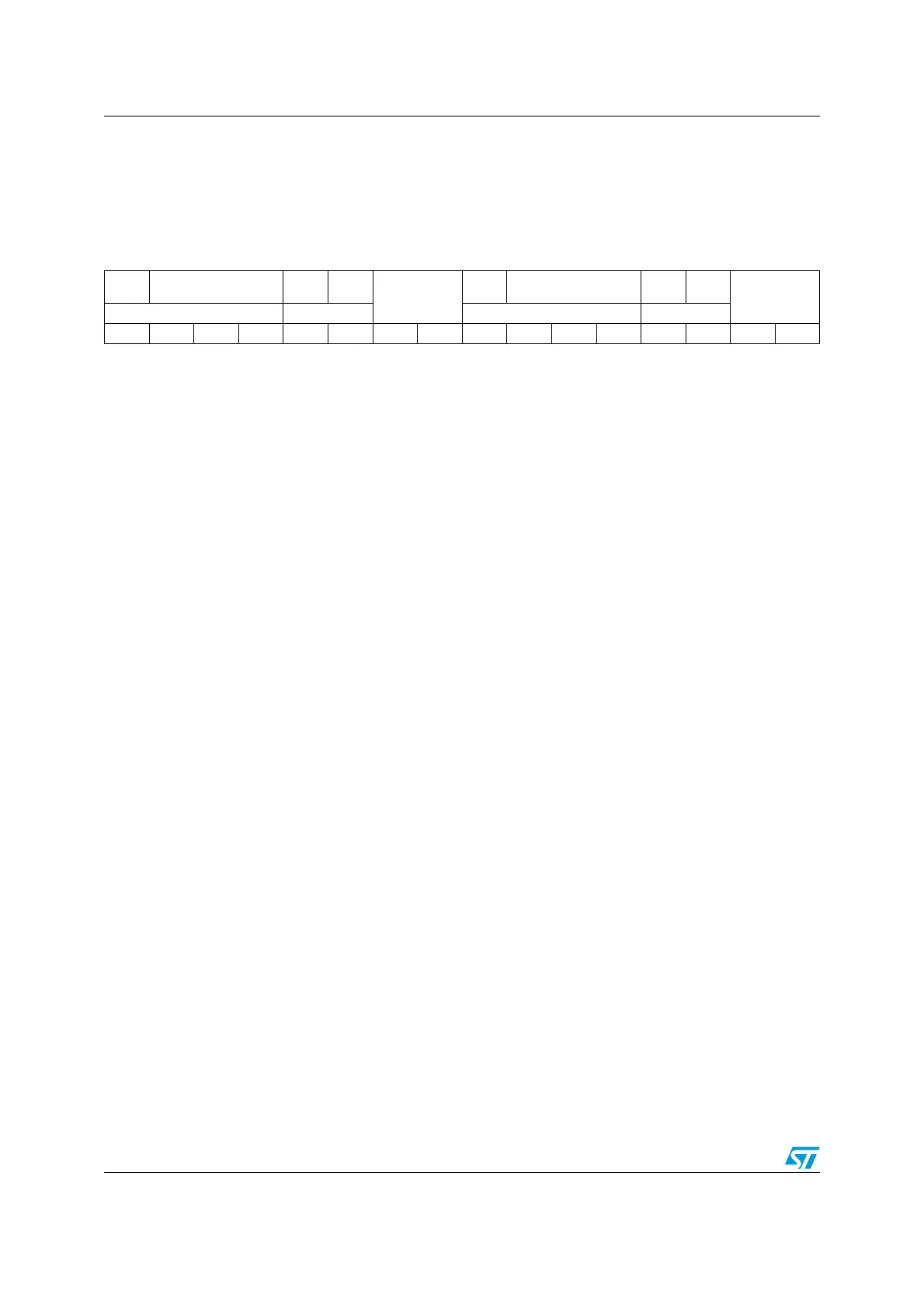

1514131211109876543210

OC4

CE

OC4M[2:0]

OC4

PE

OC4

FE

CC4S[1:0]

OC3

CE.

OC3M[2:0]

OC3

PE

OC3

FE

CC3S[1:0]

IC4F[3:0] IC4PSC[1:0] IC3F[3:0] IC3PSC[1:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bit 15 OC4CE: Output Compare 4 Clear Enable

Bits 14:12 OC4M: Output Compare 4 Mode.

Bit 11 OC4PE: Output Compare 4 Preload enable.

Bit 10 OC4FE: Output Compare 4 Fast enable.

Bits 9:8 CC4S: Capture/Compare 4 Selection.

This bit-field defines the direction of the channel (input/output) as well as the used input.

00: CC4 channel is configured as output.

01: CC4 channel is configured as input, IC4 is mapped on TI4.

10: CC4 channel is configured as input, IC4 is mapped on TI3.

11: CC4 channel is configured as input, IC4 is mapped on TRC. This mode is working only if an

internal trigger input is selected through TS bit (TIMx_SMCR register)

Note: CC4S bits are writable only when the channel is OFF (CC4E = ’0’ in TIMx_CCER).

Bit 7 OC3CE: Output Compare 3 Clear Enable

Bits 6:4 OC3M: Output Compare 3 Mode.

Bit 3 OC3PE: Output Compare 3 Preload enable.

Bit 2 OC3FE: Output Compare 3 Fast enable.

Bits 1:0 CC3S: Capture/Compare 3 Selection.

This bit-field defines the direction of the channel (input/output) as well as the used input.

00: CC3 channel is configured as output.

01: CC3 channel is configured as input, IC3 is mapped on TI3.

10: CC3 channel is configured as input, IC3 is mapped on TI4.

11: CC3 channel is configured as input, IC3 is mapped on TRC. This mode is working only if an

internal trigger input is selected through TS bit (TIMx_SMCR register)

Note: CC3S bits are writable only when the channel is OFF (CC3E = ’0’ in TIMx_CCER).

Loading...

Loading...