RM0008 Inter-integrated circuit (I

2

C) interface

591/690

The System Management Bus Specification refers to three types of devices. A slave is a

device that is receiving or responding to a command. A master is a device that issues

commands, generates the clocks, and terminates the transfer. A host is a specialized master

that provides the main interface to the system's CPU. A host must be a master-slave and

must support the SMBus host notify protocol. Only one host is allowed in a system.

Similarities between SMBus and I

2

C

● 2 wire bus protocol (1 Clk, 1 Data) + SMBus Alert line optional

● Master-slave communication, Master provides clock

● Multi master capability

● SMBus data format similar to I

2

C 7-bit addressing format (Figure 230).

Differences between SMBus and I

2

C

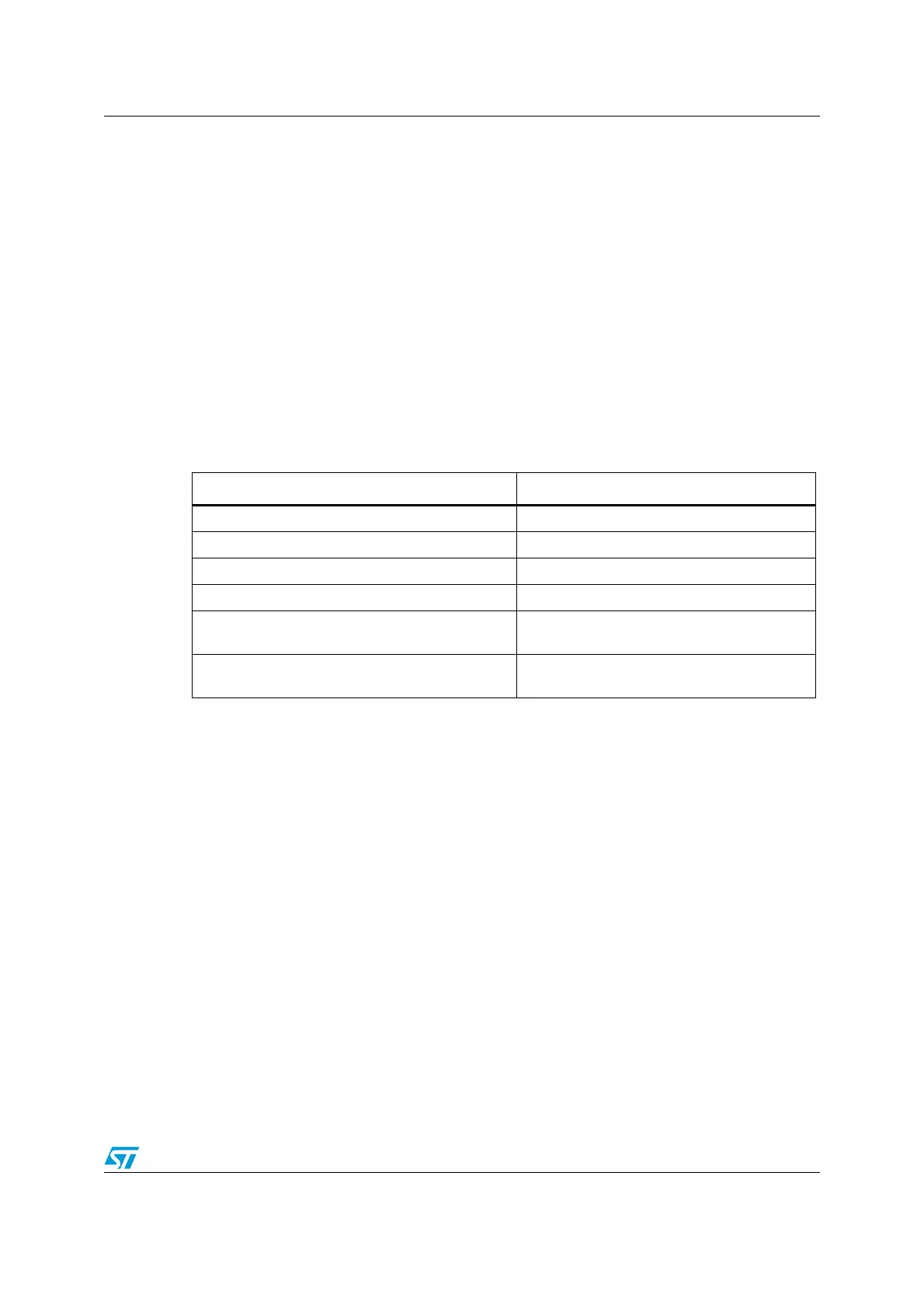

The following table describes the differences between SMBus and I

2

C.

SMBus application usage

With System Management Bus, a device can provide manufacturer information, tell the

system what its model/part number is, save its state for a suspend event, report different

types of errors, accept control parameters, and return its status. SMBus provides a control

bus for system and power management related tasks.

Device identification

Any device that exists on the System Management Bus as a slave has a unique address

called the Slave Address. For the list of reserved slave addresses, refer to the SMBus

specification ver. 2.0 (http://smbus.org/specs/).

Bus protocols

The SMBus specification supports up to 9 bus protocols. For more details of these protocols

and SMBus address types, refer to SMBus specification ver. 2.0 (http://smbus.org/specs/).

These protocols should be implemented by the user software.

Table 149. SMBus vs. I

2

C

SMBus I

2

C

Max. speed 100 kHz Max. speed 400 kHz

Min. clock speed 10 kHz No minimum clock speed

35 ms clock low timeout No timeout

Logic levels are fixed Logic levels are VDD dependent

Different address types (reserved, dynamic etc.)

7-bit, 10-bit and general call slave address

types

Different bus protocols (quick command, process

call etc.)

No bus protocols

Loading...

Loading...