Flexible static memory controller (FSMC) RM0008

400/690

16-bit NAND Flash

There is no theoretical capacity limitation as the FSMC can manage as many address

cycles as needed.

18.6.2 NAND Flash / PC Card supported memories and transactions

Tabl e 9 9 below shows the supported devices, access modes and transactions. Transactions

not allowed (or not supported) by the NAND Flash / PC Card controller appear in gray.

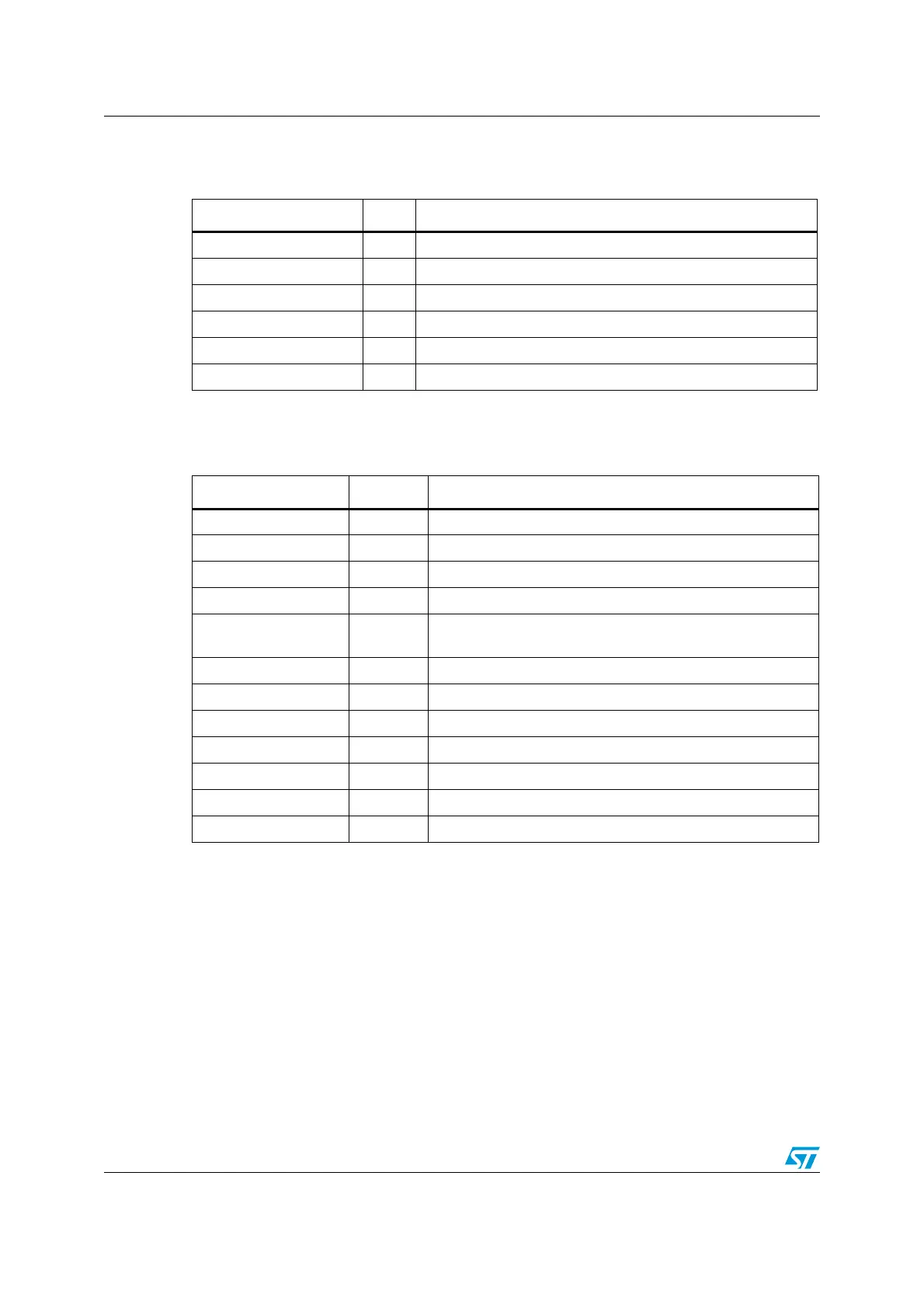

Table 97. 16-bit NAND Flash

FSMC signal name I/O Function

A[17] O NAND Flash address latch enable (ALE) signal

A[16] O NAND Flash command latch enable (CLE) signal

D[15:0] I/O 16-bit multiplexed, bidirectional address/data bus

NOE(= NRE) O Output enable (memory signal name: read enable, NRE)

NWE O Write enable

NWAIT I NAND Flash ready/busy input signal to the FSMC

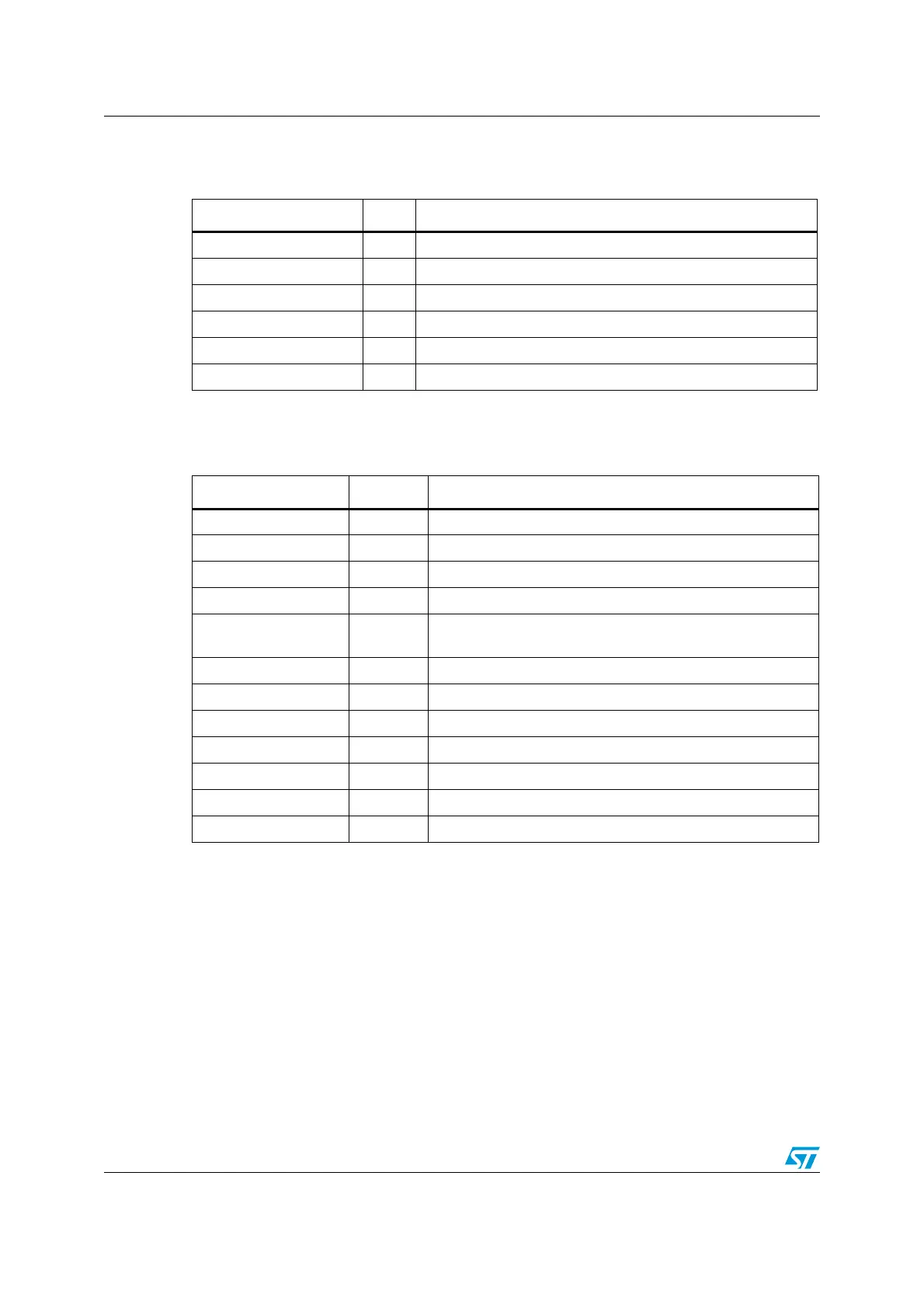

Table 98. 16-bit PC Card

FSMC signal name I/O Function

A[10:0] O Address bus

NIOS16 I Data transfer width in I/O space (16-bit or 8-bit transfer)

NIORD O Output enable for I/O space

NIOWR O Write enable for I/O space

NREG O

Register signal indicating if access is in Common or Attribute

space

D[15:0] I/O Bidirectional databus

NCE4_1 O Chip select 1

NCE4_2 O Chip select 2 (indicates if access is 16-bit or 8-bit)

NOE O Output enable

NWE O Write enable

NWAIT I PC Card wait input signal to the FSMC

CD I PC Card presence detection

Loading...

Loading...