Flexible static memory controller (FSMC) RM0008

386/690

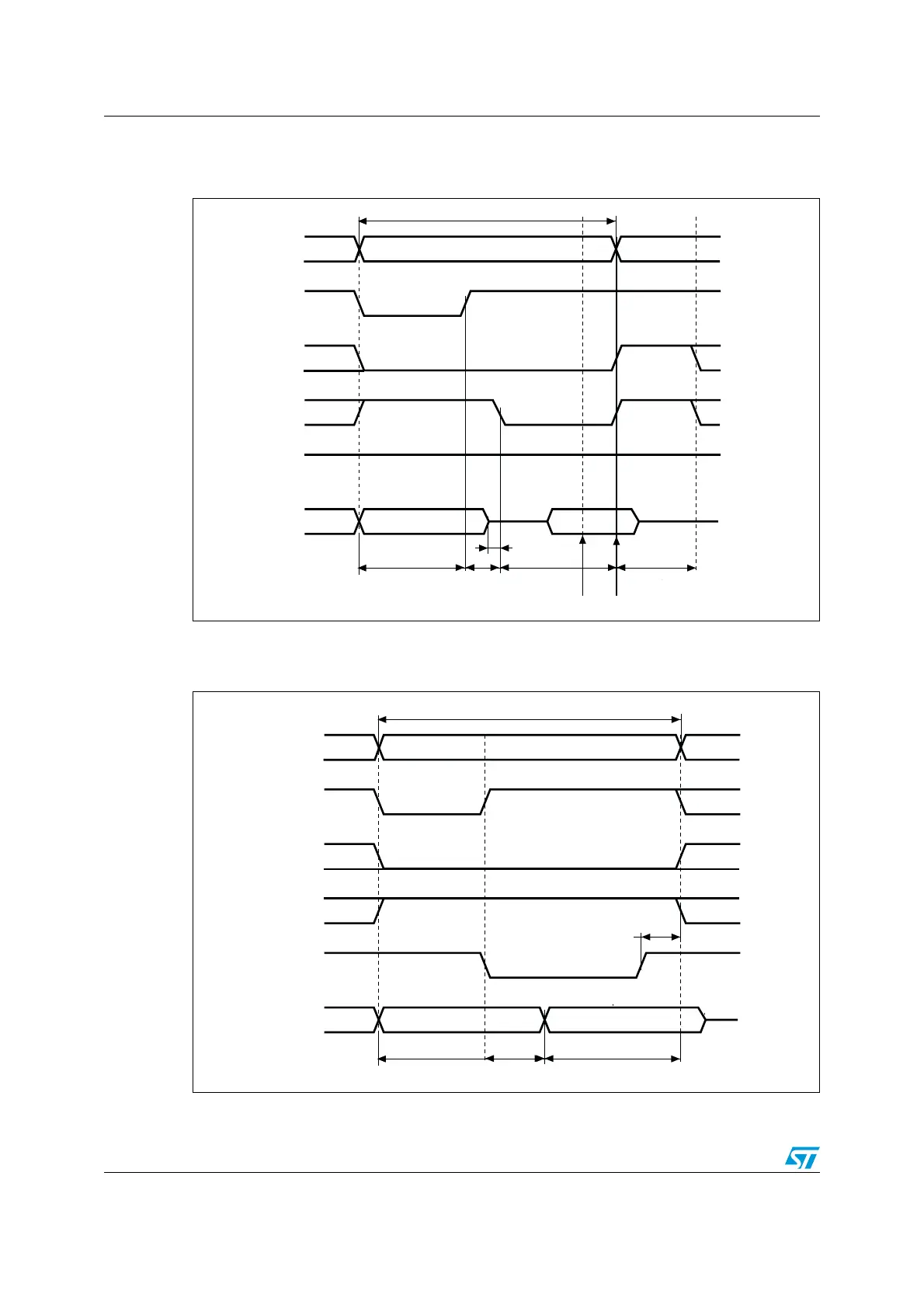

Mode muxed - asynchronous access muxed NOR Flash

Figure 170. Muxed read accesses

1. The bus turnaround delay (BUSTURN + 1) and the delay between side-by-side transactions overlap, so

BUSTURN ≤5 has not impact.

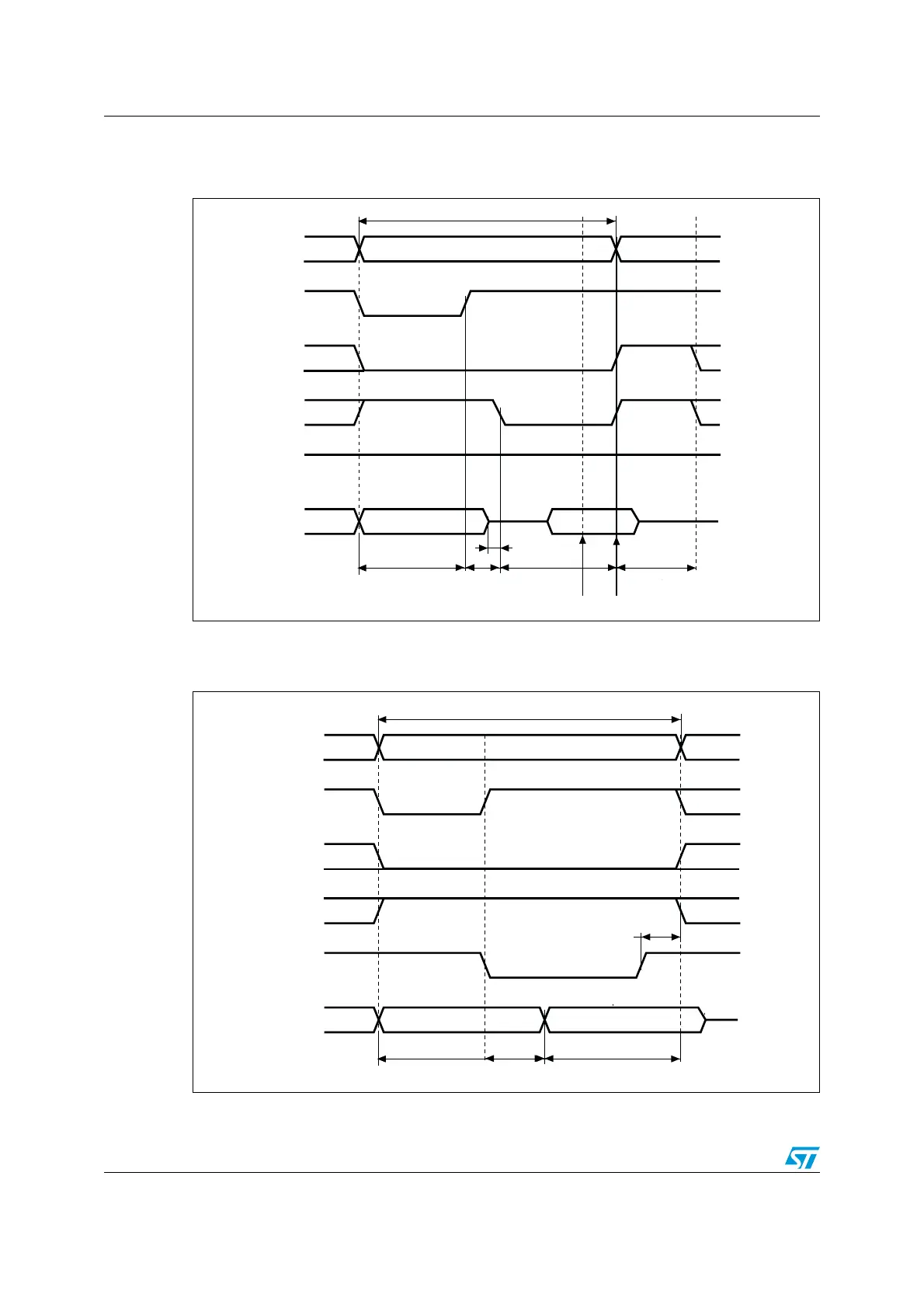

Figure 171. Muxed write accesses

The difference with mode D is the drive of the lower address byte(s) on the databus.

A[25:16]

NOE

(ADDSET +1) (DATAST + 1)

Memory transaction

Data strobe

NEx

AD[15:0]

HCLK cycles HCLK cycles

NWE

NADV

data driven

by memory

ai14728c

High

(ADDHLD + 1)

HCLK cycles

Lower address

(BUSTURN + 1)

(1)

HCLK cycles

2 HCLK

cycles

Data sampled

1HCLK cycle

A[25:16]

NOE

(ADDSET +1) (DATAST + 2)

Memory transaction

NEx

AD[15:0]

HCLK cycles HCLK cycles

NWE

NADV

data driven by FSMC

ai14729c

1HCLK

ADDHLD

HCLK cycles

Lower address

Loading...

Loading...