Universal synchronous asynchronous receiver transmitter (USART) RM0008

636/690

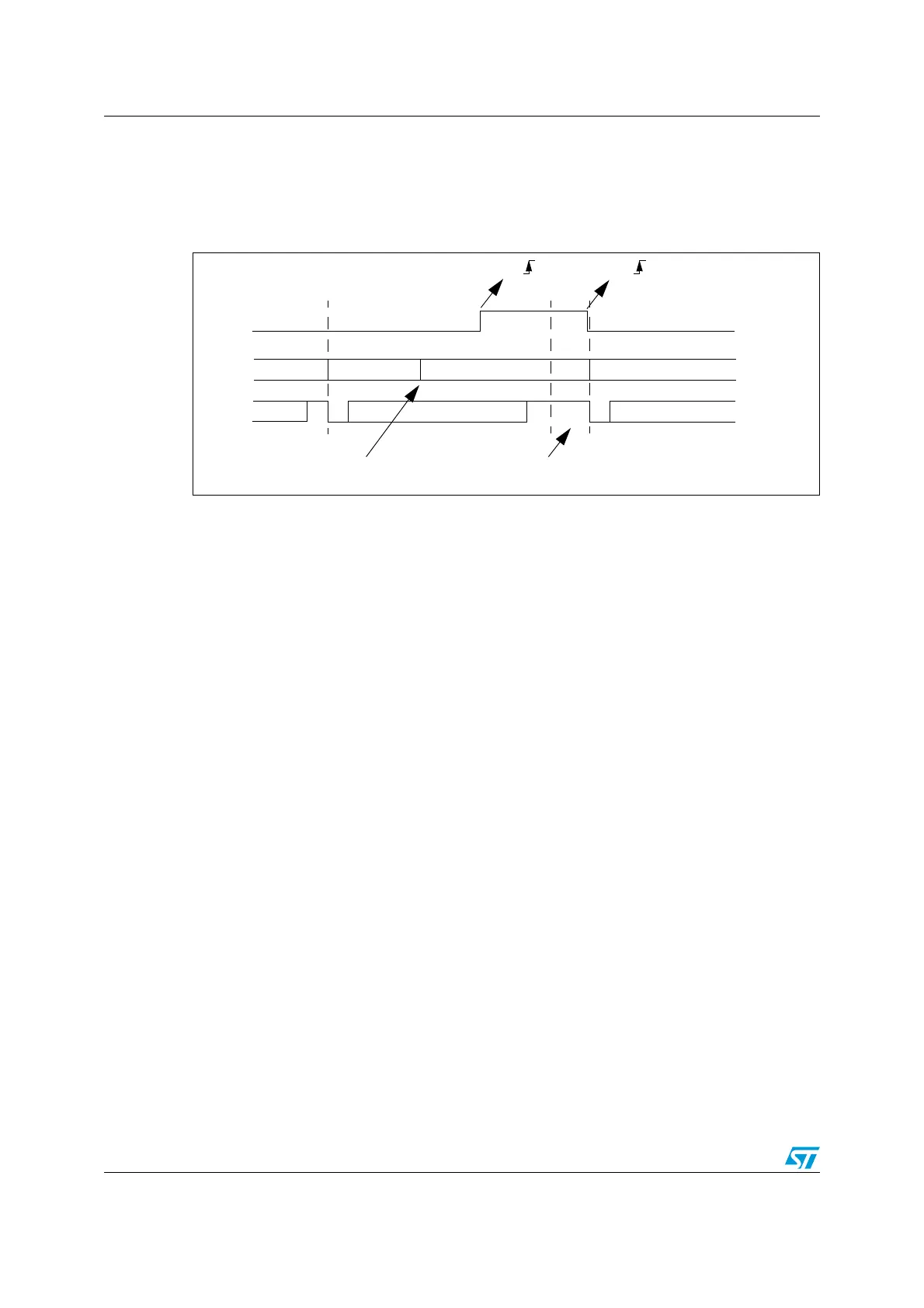

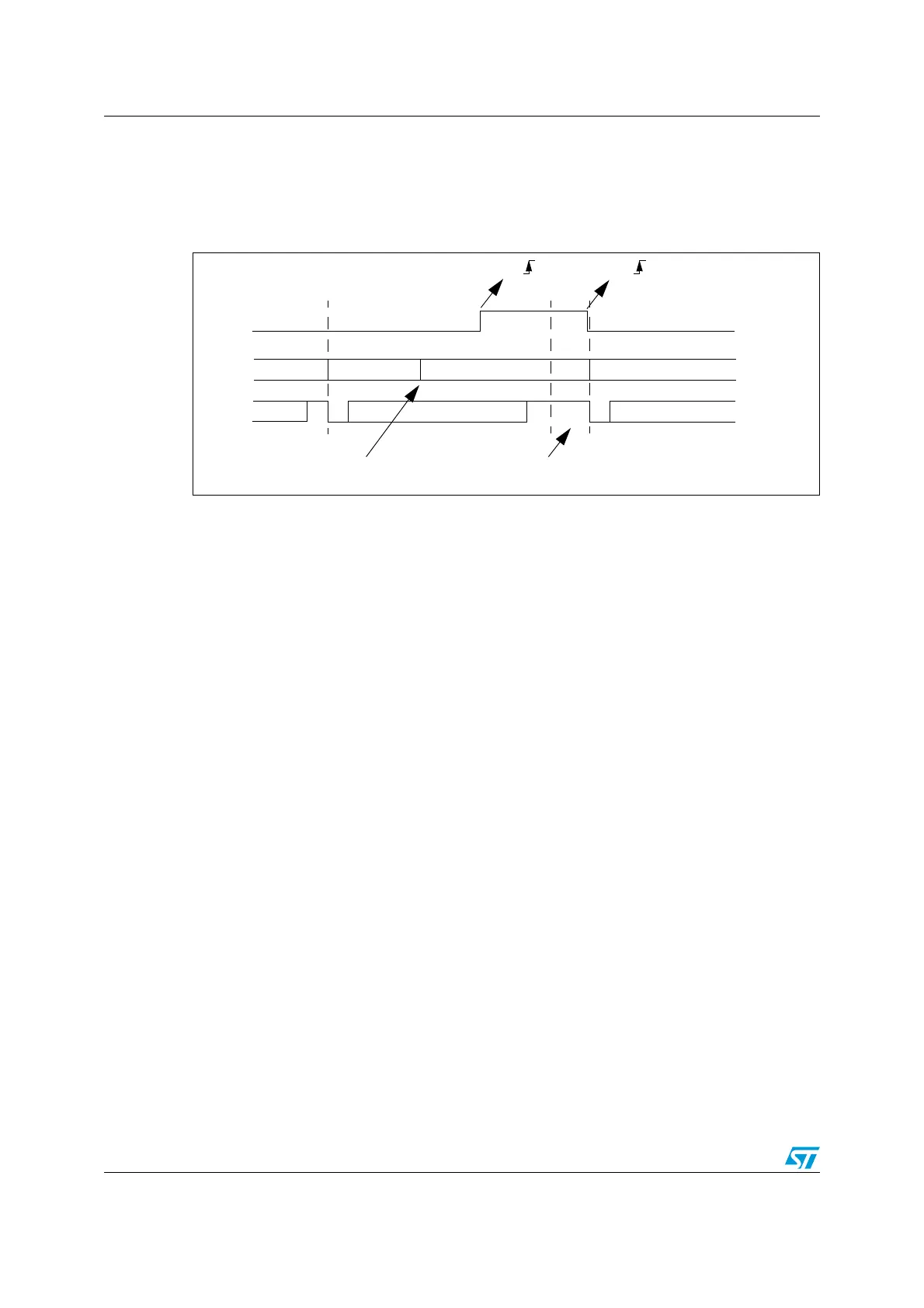

When CTSE=1, the CTSIF status bit is automatically set by hardware as soon as the nCTS

input toggles. It indicates when the receiver becomes ready or not ready for communication.

An interrupt is generated if the CTSIE bit in the USART_CR3 register is set. The figure

below shows an example of communication with CTS flow control enabled.

Figure 256. CTS flow control

Start

Bit

Stop

Bit

Data 2 Idle

Start

Bit

Data 3

TX

nCTS

CTS

Transmission of Data 3

Data 1

Stop

Bit

is delayed until nCTS = 0

CTS

Data 2 Data 3empty empty

Transmit data register

TDR

Writing data 3 in TDR

Loading...

Loading...