DMA controller (DMA) RM0008

138/690

9.3.5 Interrupts

An interrupt can be produced on a Half-transfer, Transfer complete or Transfer error for each

DMA channel. Separate interrupt enable bits are available for flexibility.

Note: In high-density devices DMA2 Channel4 and DMA2 Channel5 interrupts are mapped onto

the same interrupt vector. All other DMA1 and DMA2 Channel interrupts have their own

interrupt vector.

9.3.6 DMA request mapping

DMA1 controller

The 7 requests from the peripherals (TIMx[1,2,3,4], ADC1, SPI1, SPI/I2S2, I2Cx[1,2] and

USARTx[1,2,3]) are simply logically ORed before entering DMA1, this means that only one

request must be enabled at a time. Refer to Figure 19: DMA1 request mapping.

The peripheral DMA requests can be independently activated/de-activated by programming

the DMA control bit in the registers of the corresponding peripheral.

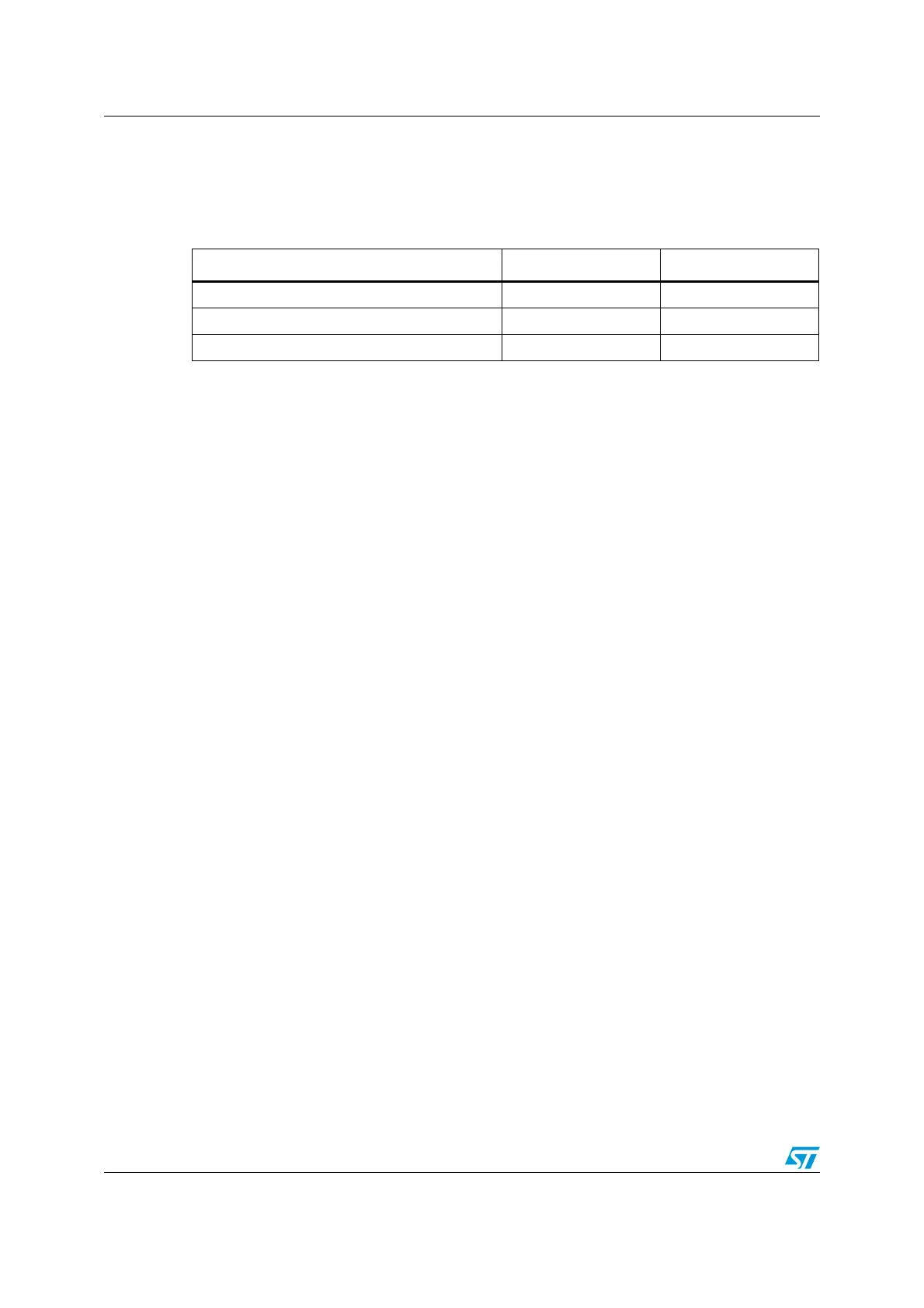

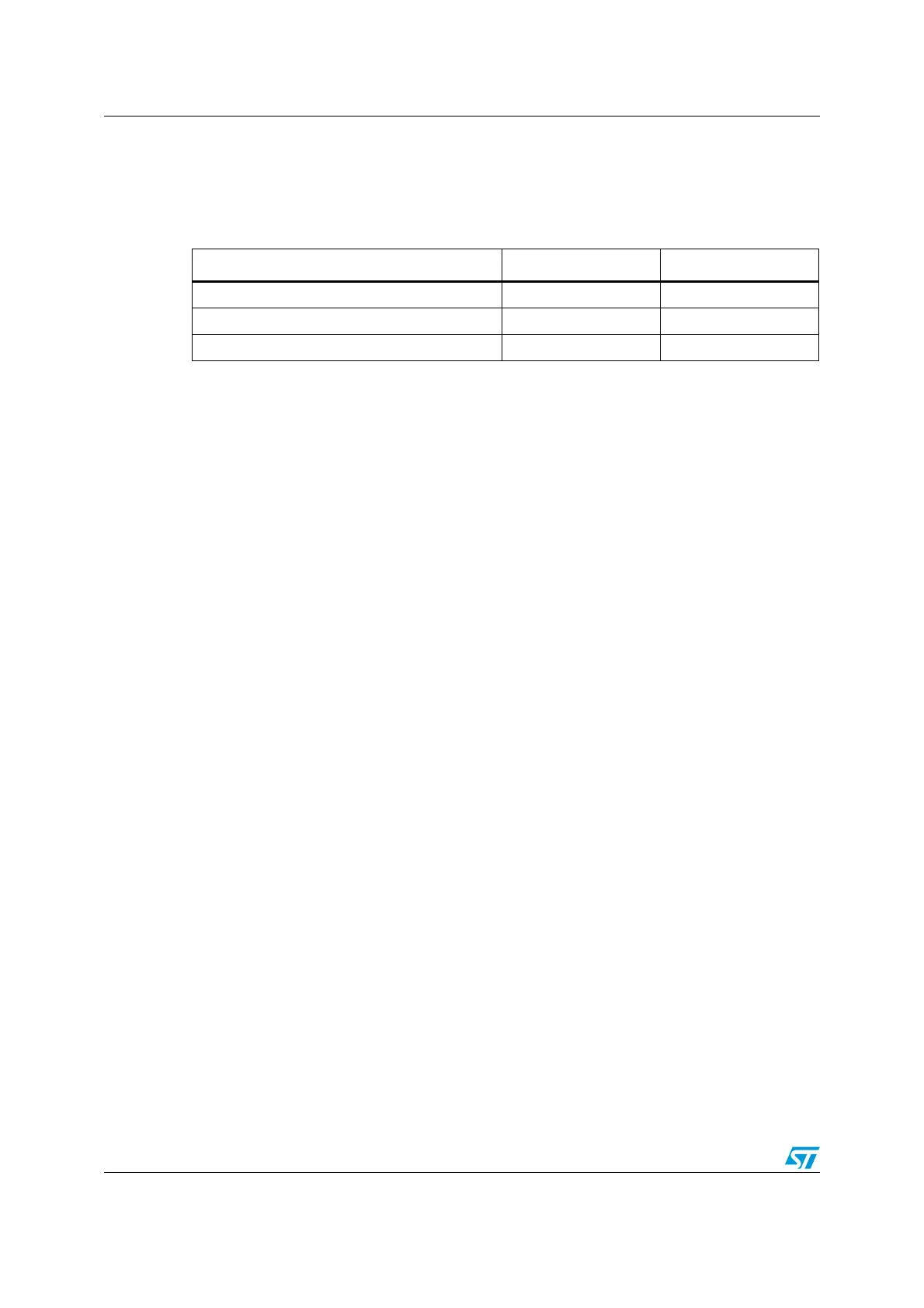

Table 38. DMA interrupt requests

Interrupt event Event flag Enable Control bit

Half-transfer HTIF HTIE

Transfer complete TCIF TCIE

Transfer error TEIF TEIE

Loading...

Loading...