RM0008 Flexible static memory controller (FSMC)

375/690

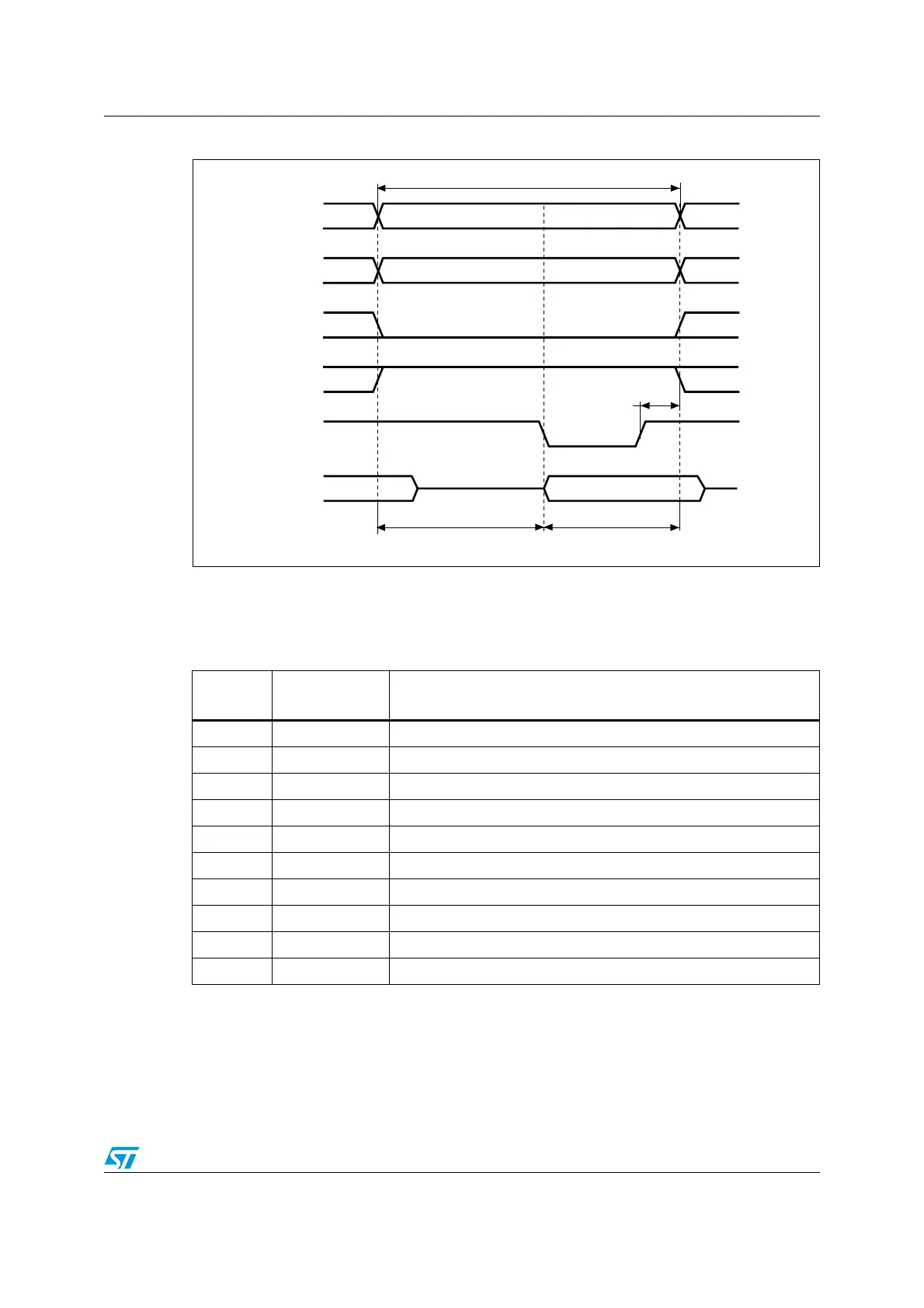

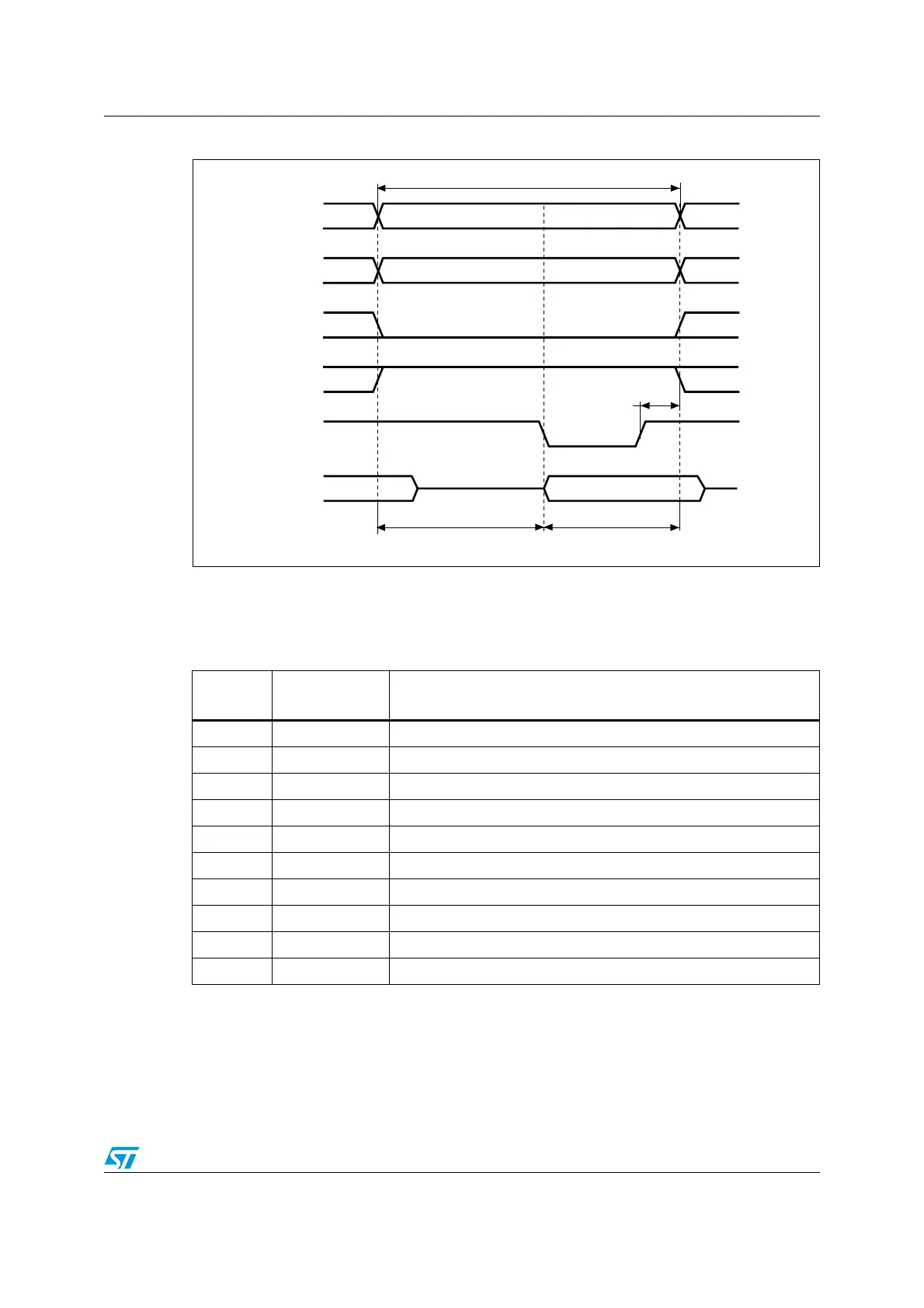

Figure 160. Mode1 write accesses

The one HCLK cycle at the end of the write transaction helps guarantee the address and

data hold time after the NWE rising edge. Due to the presence of this one HCLK cycle, the

DATAST value must be greater than zero (DATAST > 0).

Table 75. FSMC_BCRx bit fields

Bit

number

Bit name Value to set

31-15 0x0000

14-10 0x0

9 WAITPOL Meaningful only if bit 15 is 1.

8 BURSTEN 0x0

7 -

6 FACCEN -

5-4 MWID As needed

3-2 MTYP As needed, exclude 10 (NOR Flash).

1 MUXEN 0x0

0 MBKEN 0x1

A[25:0]

NOE

(ADDSET +1) (DATAST + 1)

Memory transaction

NEx

D[15:0]

HCLK cycles HCLK cycles

NWE

NBL[1:0]

data driven by FSMC

ai14721b

1HCLK

Loading...

Loading...