RM0008 Debug support (DBG)

665/690

26.8.6 SW-AP registers

Access to these registers are initiated when APnDP=1

There are many AP Registers (see AHB-AP) addressed as the combination of:

● The shifted value A[3:2]

● The current value of the DP SELECT register

26.9 AHB-AP (AHB Access Port) - valid for both JTAG-DP or SW-

DP

Features:

● System access is independent of the processor status.

● Either SW-DP or JTAG-DP accesses AHB-AP.

● The AHB-AP is an AHB master into the Bus Matrix. Consequently, it can access all the

data buses (Dcode Bus, System Bus, internal and external PPB bus) but the ICode

bus.

● Bitband transactions are supported.

● AHB-AP transactions bypass the FPB.

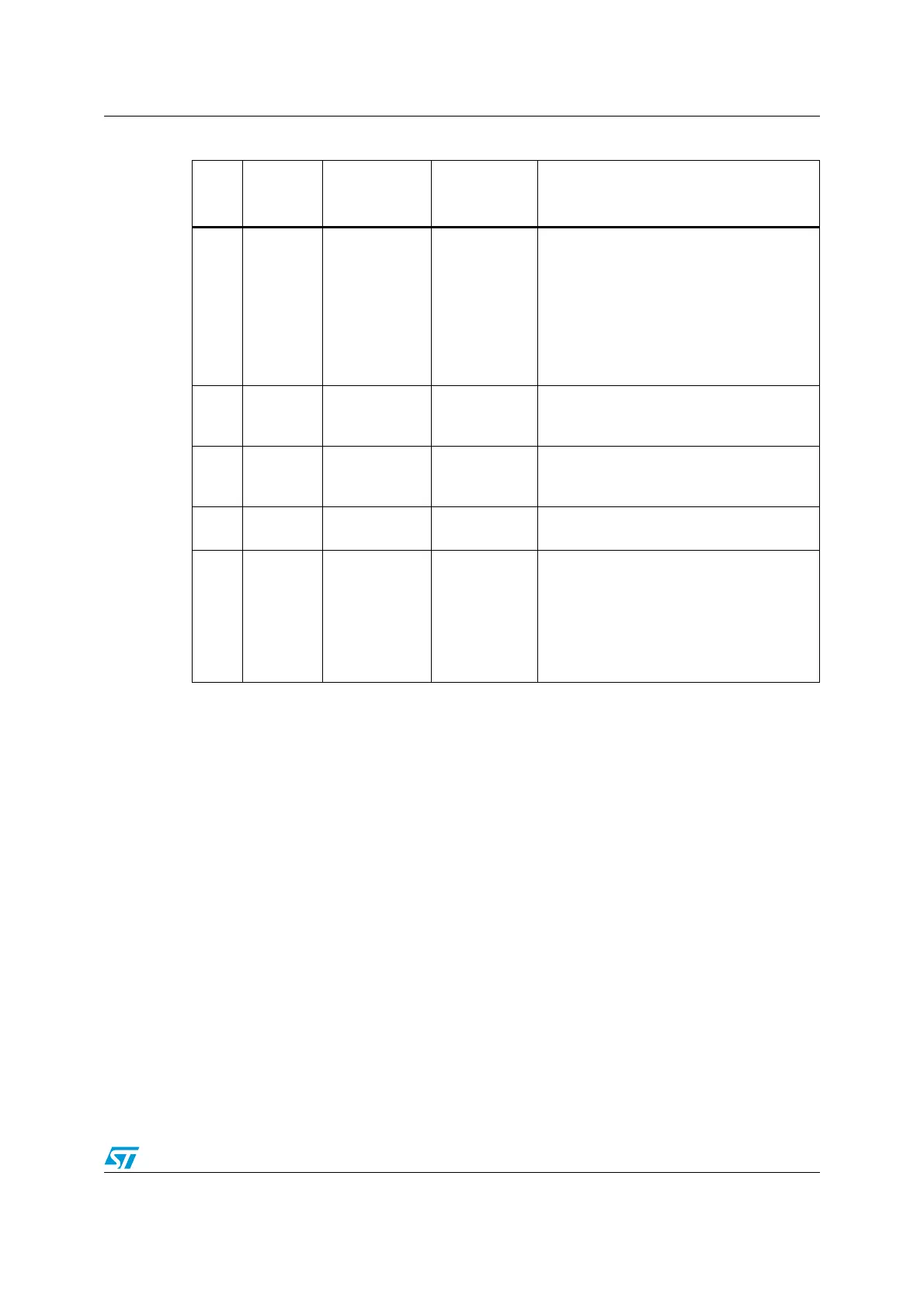

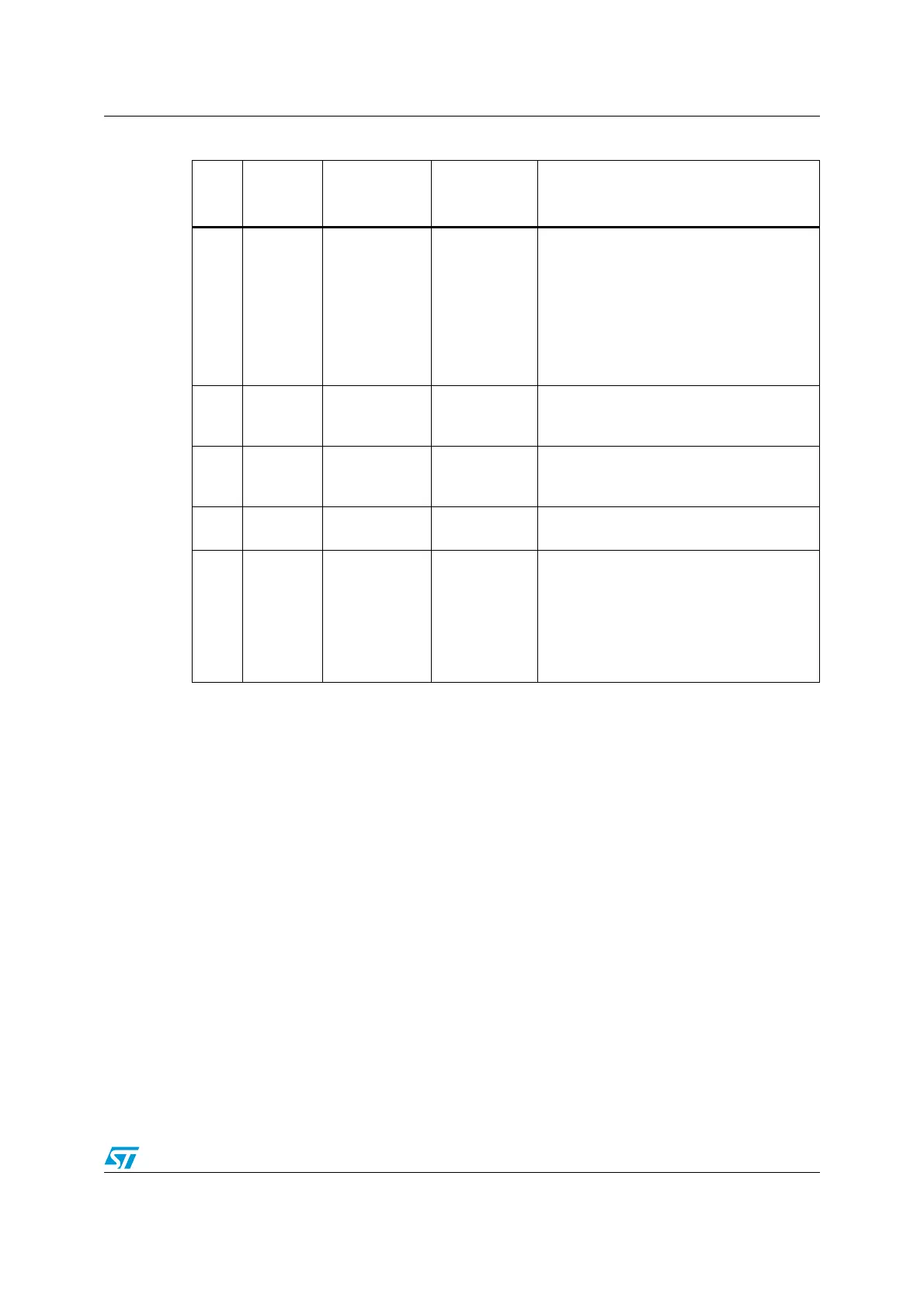

01 Read/Write 0 DP-CTRL/STAT

Purpose is to:

– request a system or debug power-up

– configure the transfer operation for AP

accesses

– control the pushed compare and pushed

verify operations.

– read some status flags (overrun, power-up

acknowledges)

01 Read/Write 1

WIRE

CONTROL

Purpose is to configure the physical serial

port protocol (like the duration of the

turnaround time)

10 Read

READ

RESEND

Enables recovery of the read data from a

corrupted debugger transfer, without

repeating the original AP transfer.

10 Write SELECT

The purpose is to select the current access

port and the active 4-words register window

11 Read/Write

READ

BUFFER

This read buffer is useful because AP

accesses are posted (the result of a read AP

request is available on the next AP

transaction),

This read buffer captures data from the AP,

presented as the result of a previous read,

without initiating a new transaction

Table 165. SW-DP registers (continued)

A(3:2) R/W

CTRLSEL bit

of SELECT

register

Register Notes

Loading...

Loading...