General-purpose timer (TIMx) RM0008

282/690

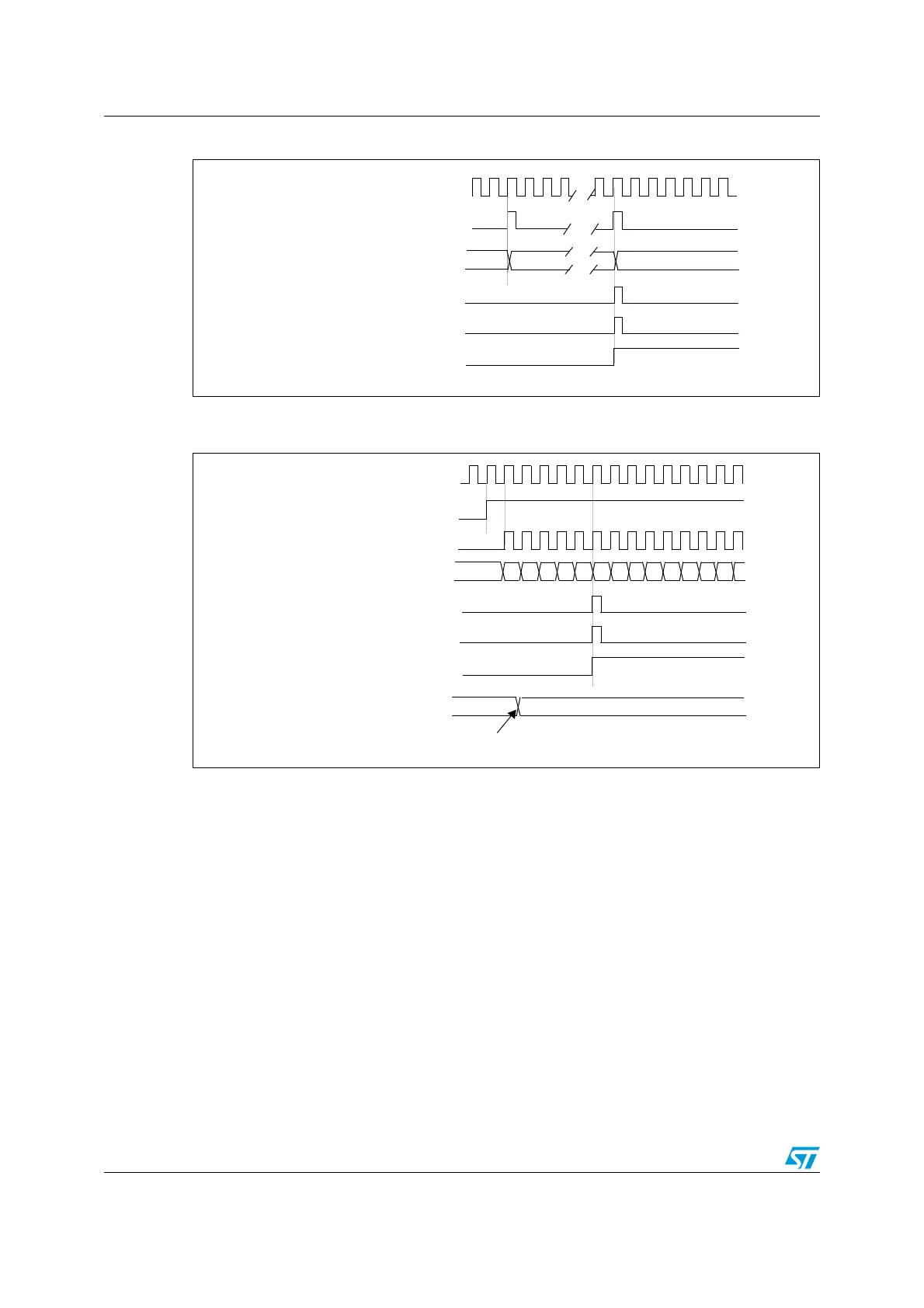

Figure 107. Counter timing diagram, internal clock divided by N

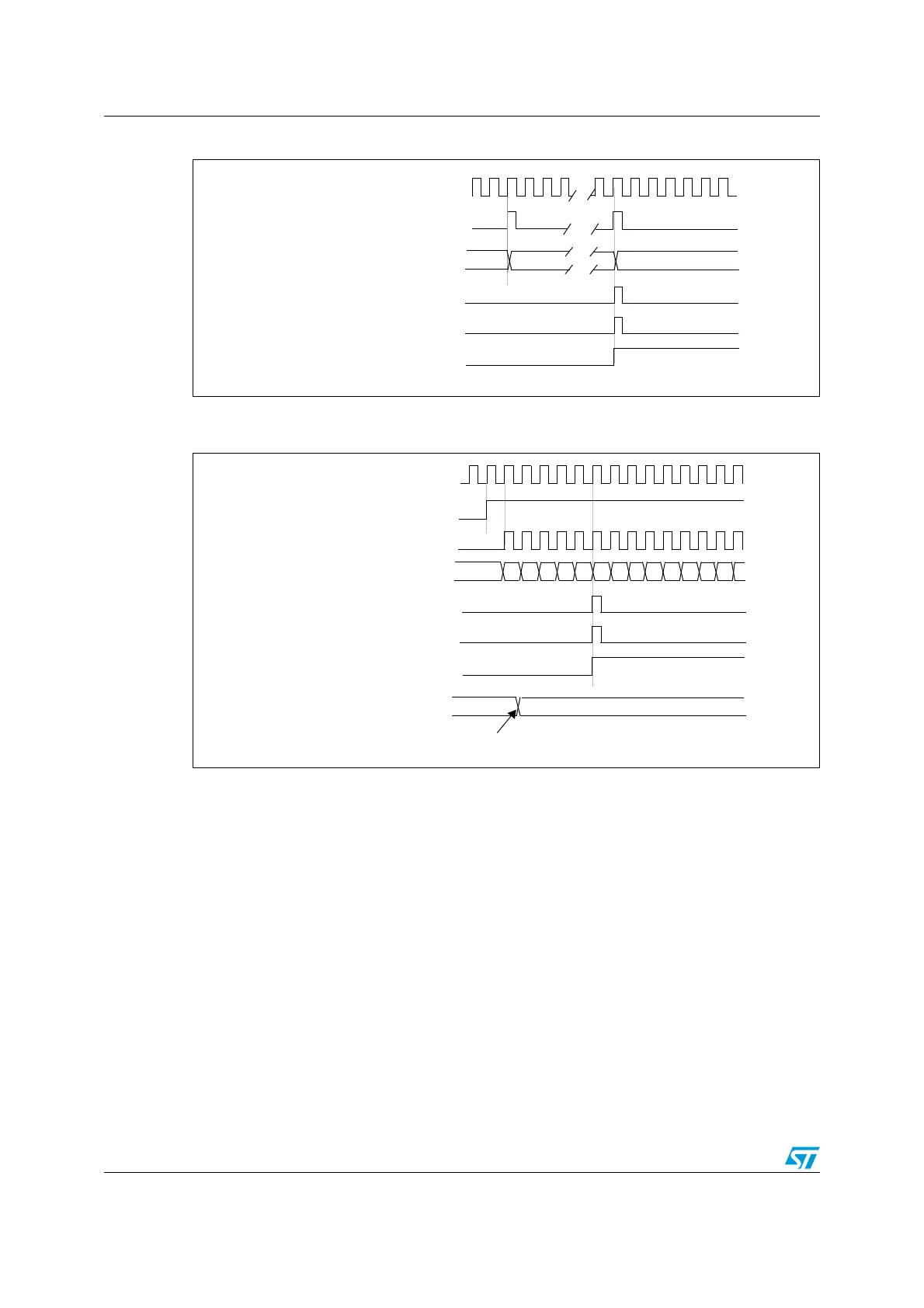

Figure 108. Counter timing diagram, Update event when repetition counter is not

used

Center-aligned mode (up/down counting)

In center-aligned mode, the counter counts from 0 to the auto-reload value (content of the

TIMx_ARR register) – 1, generates a counter overflow event, then counts from the auto-

reload value down to 1 and generates a counter underflow event. Then it restarts counting

from 0.

In this mode, the direction bit (DIR from TIMx_CR1 register) cannot be written. It is updated

by hardware and gives the current direction of the counter.

The update event can be generated at each counter overflow and at each counter underflow

or by setting the UG bit in the TIMx_EGR register (by software or by using the slave mode

controller) also generates an update event. In this case, the counter restarts counting from

0, as well as the counter of the prescaler.

The UEV update event can be disabled by software by setting the UDIS bit in TIMx_CR1

register. This is to avoid updating the shadow registers while writing new values in the

preload registers. Then no update event occurs until the UDIS bit has been written to 0.

However, the counter continues counting up and down, based on the current auto-reload

value.

Timer clock = CK_CNT

Counter register

36

20

1F

Update interrupt flag (UIF)

Counter underflow

Update event (UEV)

CK_INT

00

36

CNT_EN

Timer clock = CK_CNT

Counter register

Update interrupt flag (UIF)

Counter underflow

Update event (UEV)

35 34 33 32 31 30 2F04 03 02 01 0005

Auto-reload register

FF 36

Write a new value in TIMx_ARR

CK_INT

Loading...

Loading...