RM0008 SDIO interface (SDIO)

463/690

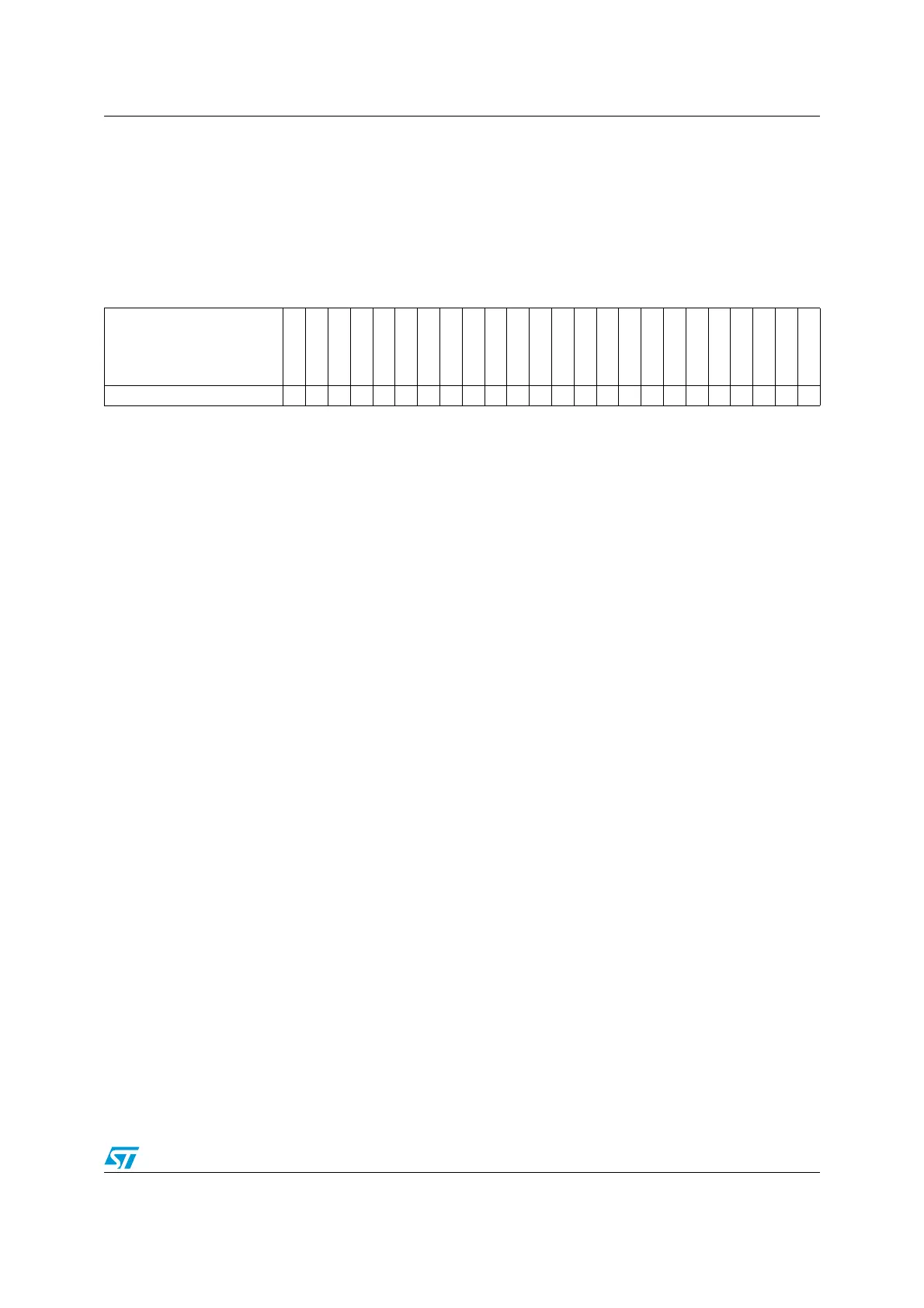

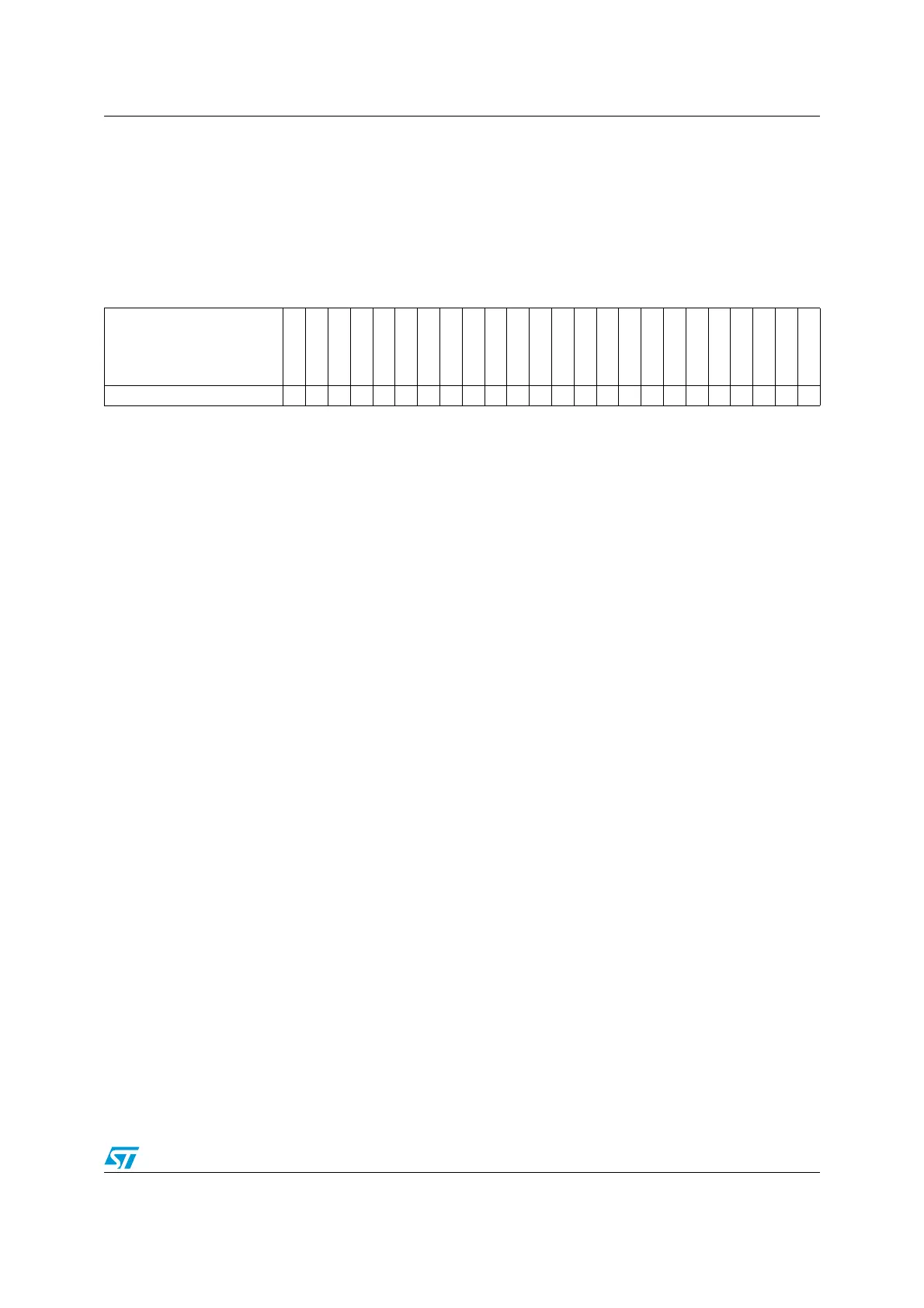

19.9.13 SDIO Mask Register (SDIO_MASK)

Address offset: 0x3C

Reset value: 0x0000 0000

The interrupt mask register determines which status flags generate an interrupt request by

setting the corresponding bit to 1b.

313029282726252423222120191817161514131211109876543210

Reserved

CEATAENDIE

SDIOITIE

RXDAVLIE

TXDAVLIE

RXFIFOEIE

TXFIFOEIE

RXFIFOFIE

TXFIFOFIE

RXFIFOHFIE

TXFIFOHEIE

RXACTIE

TXACTIE

CMDACTIE

DBCKENDIE

STBITERRIE

DATAENDIE

CMDSENTIE

CMDRENDIE

RXOVERRIE

TXUNDERRIE

DTIMEOUTIE

CTIMEOUTIE

DCRCFAILIE

CCRCFAILIE

Res. r/w r/w r/w r/w r/w r/w r/w r/w r/w r/w r/w r/w r/w r/w r/w r/w r/w r/w r/w r/w r/w r/w r/w r/w

Bits 31:24 Reserved, always read as 0.

Bit 23 CEATAENDIE: CE-ATA command completion signal received Interrupt Enable

Set and reset by software to enable/disable the interrupt generated when receiving the CE-ATA

command completion signal.

0: CE-ATA command completion signal received interrupt disabled

1: CE-ATA command completion signal received interrupt enabled

Bit 22 SDIOITIE: SDIO Mode Interrupt Received Interrupt Enable

Set and reset by software to enable/disable the interrupt generated when receiving the SDIO mode

interrupt.

0: SDIO Mode Interrupt Received interrupt disabled

1: SDIO Mode Interrupt Received interrupt enabled

Bit 21 RXDAVLIE: Data available in Rx FIFO Interrupt Enable

Set and reset by software to enable/disable the interrupt generated by the presence of data

available in Rx FIFO.

0: Data available in Rx FIFO interrupt disabled

1: Data available in Rx FIFO interrupt enabled

Bit 20 TXDAVLIE: Data available in Tx FIFO Interrupt Enable

Set and reset by software to enable/disable the interrupt generated by the presence of data

available in Tx FIFO.

0: Data available in Tx FIFO interrupt disabled

1: Data available in Tx FIFO interrupt enabled

Bit 19 RXFIFOEIE: Rx FIFO Empty Interrupt Enable

Set and reset by software to enable/disable interrupt caused by Rx FIFO empty.

0: Rx FIFO empty interrupt disabled

1: Rx FIFO empty interrupt enabled

Bit 18 TXFIFOEIE: Tx FIFO Empty Interrupt Enable

Set and reset by software to enable/disable interrupt caused by Tx FIFO empty.

0: Tx FIFO empty interrupt disabled

1: Tx FIFO empty interrupt enabled

Bit 17 RXFIFOFIE: Rx FIFO Full Interrupt Enable

Set and reset by software to enable/disable interrupt caused by Rx FIFO full.

0: Rx FIFO full interrupt disabled

1: Rx FIFO full interrupt enabled

Loading...

Loading...