Window watchdog (WWDG) RM0008

364/690

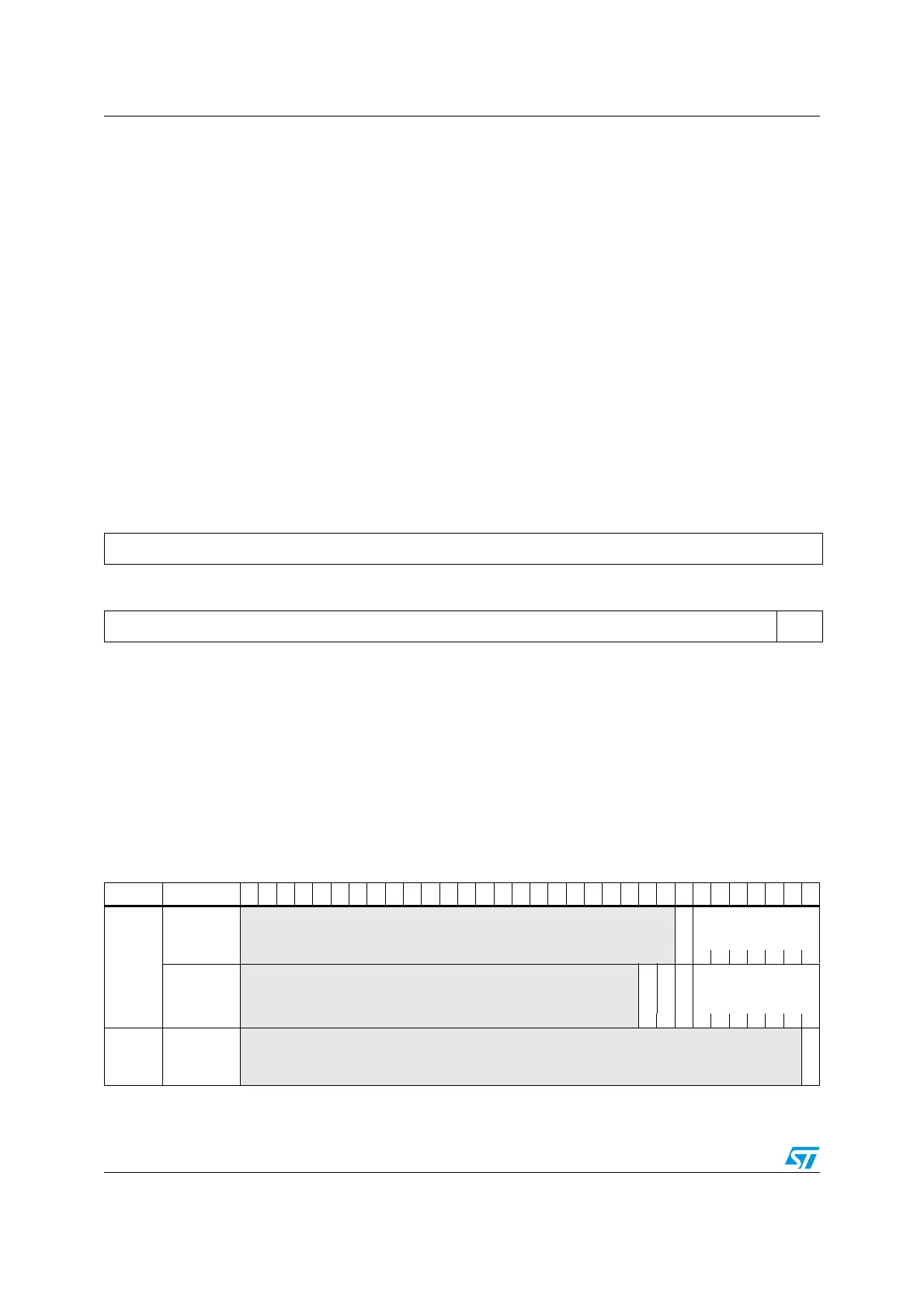

17.6.3 Status register (WWDG_SR)

Address offset: 0x08

Reset value: 0x00

17.6.4 WWDG register map

The following table gives the WWDG register map and reset values.

Refer to Table 1 on page 36 for the register boundary addresses.

Bit 31:10 Reserved

Bit 9 EWI: Early Wakeup Interrupt

When set, an interrupt occurs whenever the counter reaches the value 40h. This interrupt is only

cleared by hardware after a reset.

Bits 8:7 WDGTB[1:0]: Timer Base

The time base of the prescaler can be modified as follows:

00: CK Counter Clock (PCLK1 div 4096) div 1

01: CK Counter Clock (PCLK1 div 4096) div 2

10: CK Counter Clock (PCLK1 div 4096) div 4

11: CK Counter Clock (PCLK1 div 4096) div 8

Bits 6:0 W[6:0] 7-bit window value

These bits contain the window value to be compared to the downcounter.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved EWIF

Res. rc_w0

Bit 31:1Reserved

Bit 0 EWIF: Early Wakeup Interrupt Flag

This bit is set by hardware when the counter has reached the value 40h. It must be cleared by

software by writing ‘0’. A write of ‘1’ has no effect. This bit is also set if the interrupt is not enabled.

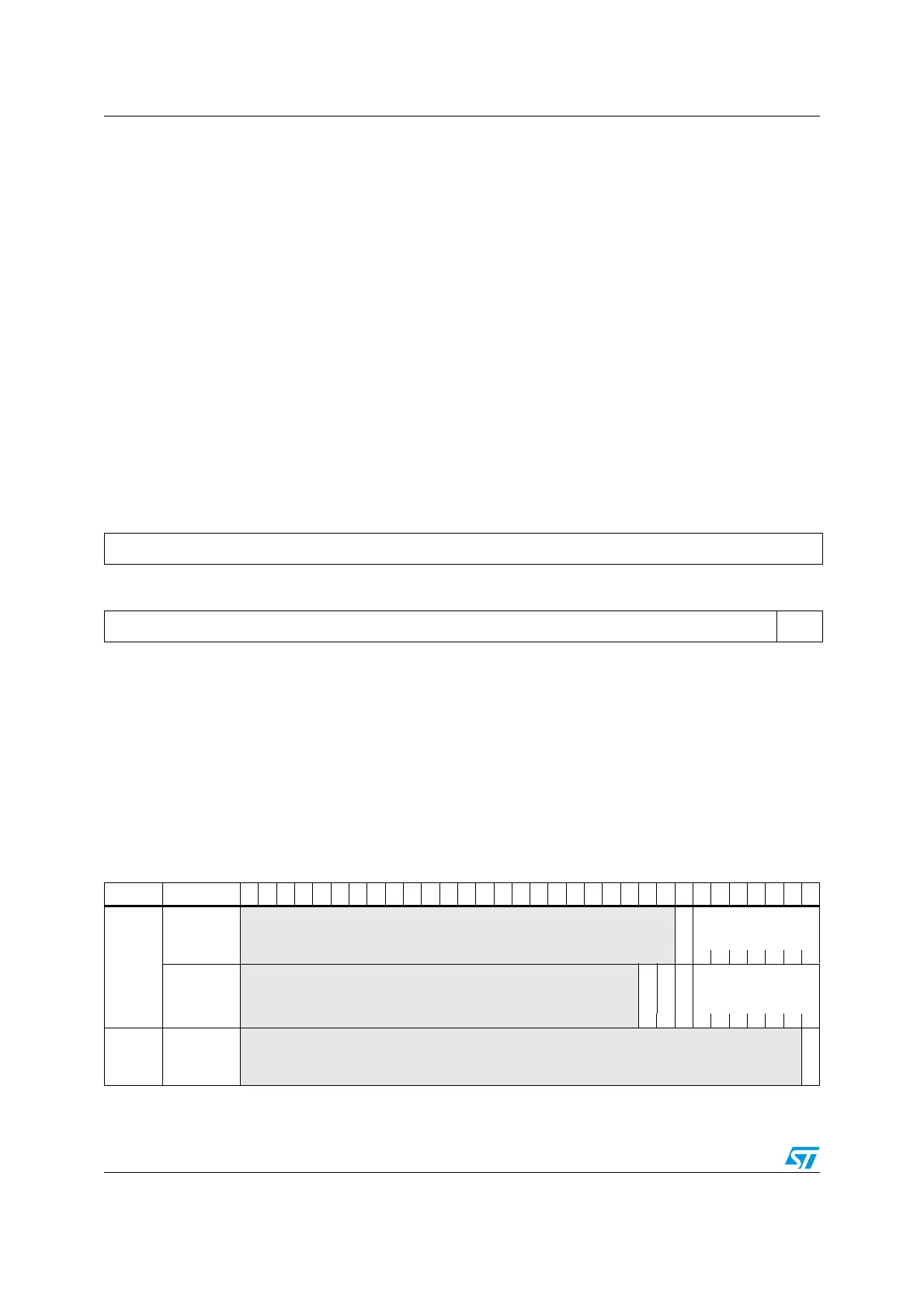

Table 65. WWDG register map and reset values

Offset Register

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0x00

WWDG_CR

Reserved

WDGA

T[6:0]

Reset value 01111111

0x04

WWDG_CFR

Reserved

EWI

WDGTB1

WDGTB0

W[6:0]

Reset value 0001111111

0x08

WWDG_SR

Reserved

EWIF

Reset value 0

Loading...

Loading...