RM0008 Window watchdog (WWDG)

363/690

17.5 Debug mode

When the microcontroller enters debug mode (Cortex-M3 core halted), the WWDG counter

either continues to work normally or stops, depending on DBG_WWDG_STOP configuration

bit in DBG module. For more details, refer to Section 26.15.2: Debug support for timers,

watchdog, bxCAN and I2C.

17.6 Debug registers

Refer to Section 1.1 on page 32 for a list of abbreviations used in register descriptions.

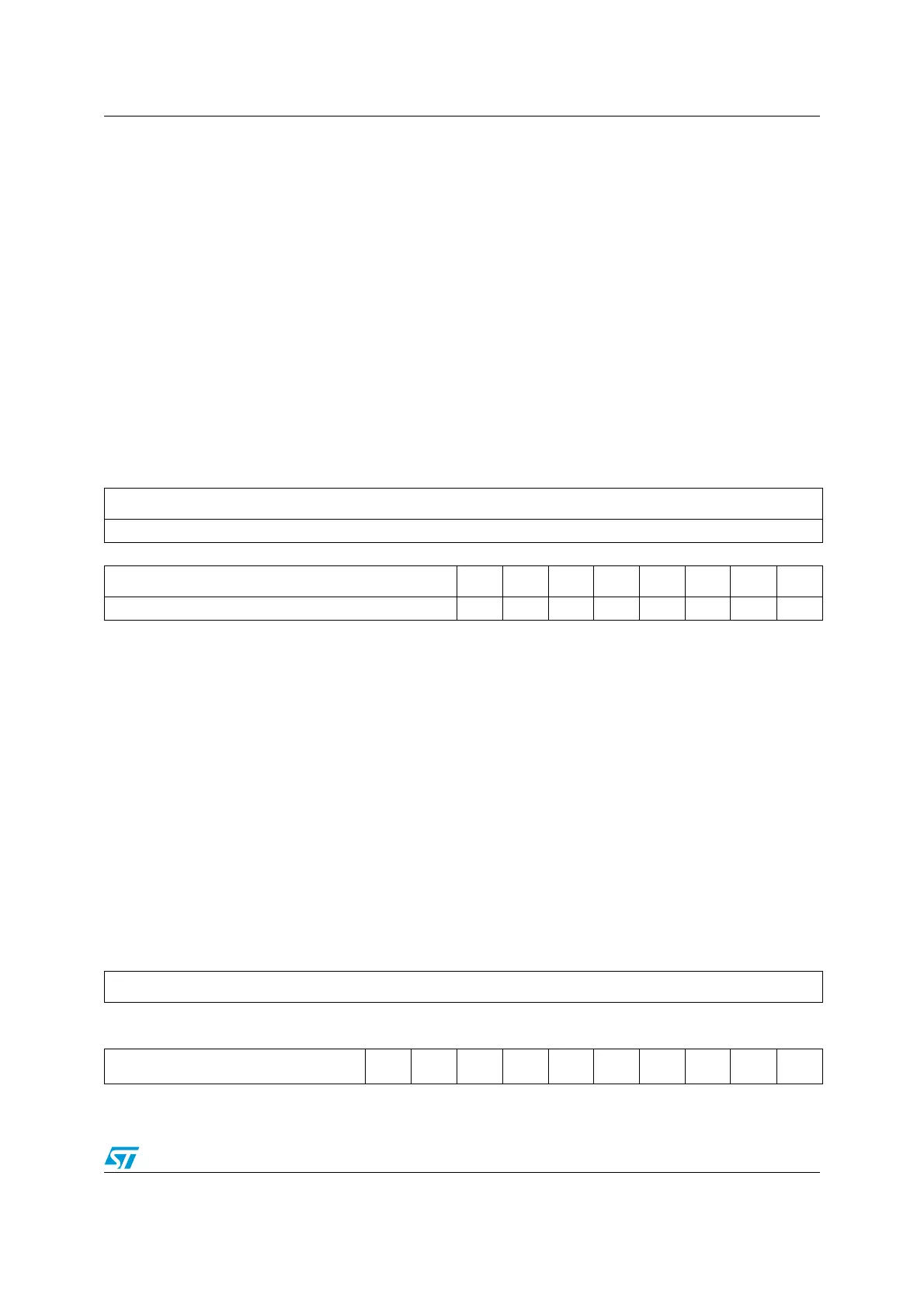

17.6.1 Control Register (WWDG_CR)

Address offset: 0x00

Reset value: 0x7F

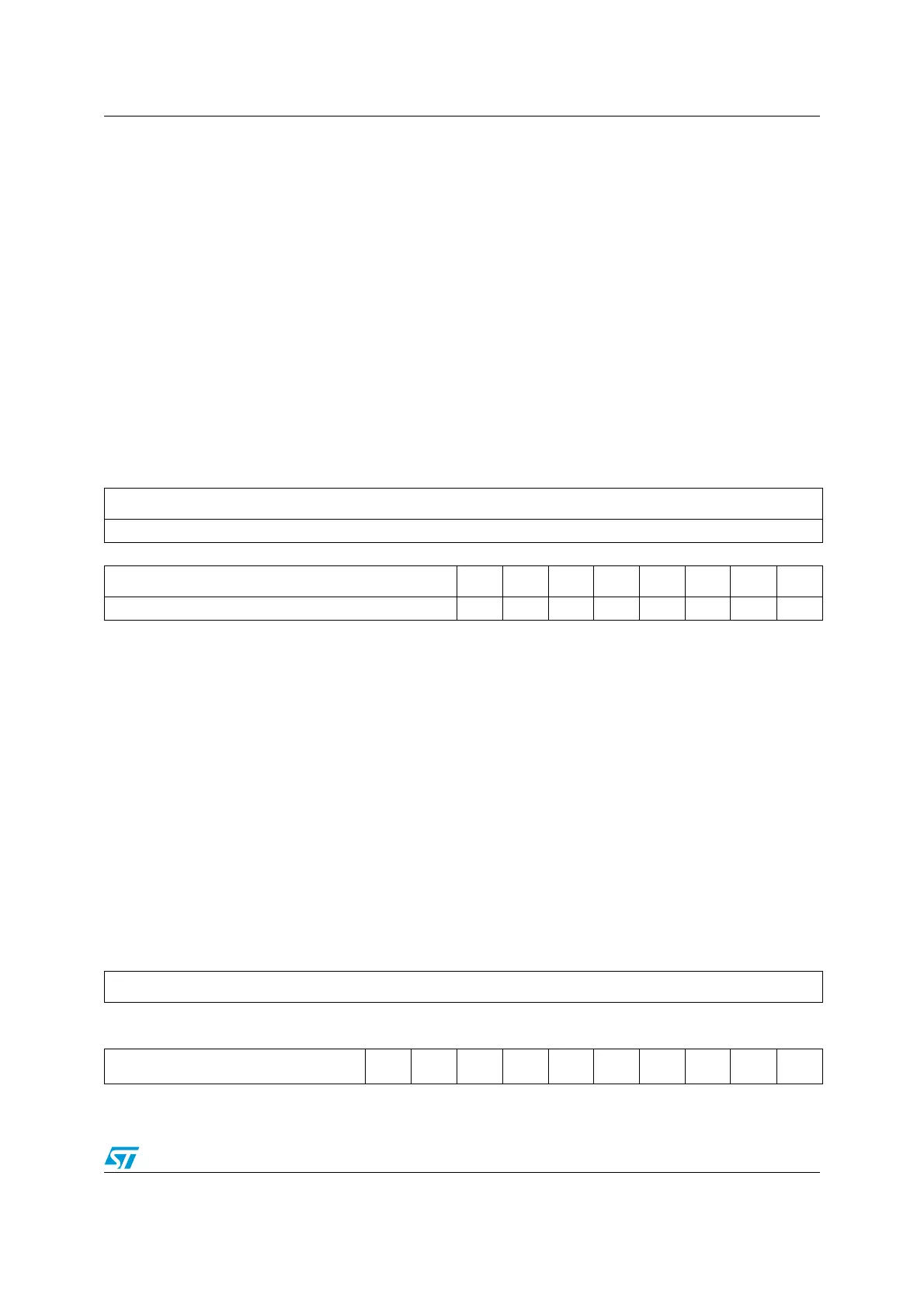

17.6.2 Configuration register (WWDG_CFR)

Address offset: 0x04

Reset value: 0x7F

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved WDGA T6 T5 T4 T3 T2 T1 T0

Res. rs rw rw rw rw rw rw rw

Bits 31:8 Reserved

Bit 7 WDGA: Activation bit

This bit is set by software and only cleared by hardware after a reset. When WDGA = 1, the

watchdog can generate a reset.

0: Watchdog disabled

1: Watchdog enabled

Bits 6:0 T[6:0]: 7-bit counter (MSB to LSB).

These bits contain the value of the watchdog counter. It is decremented every (4096 x 2

WDGTB

)

PCLK1 cycles. A reset is produced when it rolls over from 40h to 3Fh (T6 becomes cleared).

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved EWI

WDG

TB1

WDG

TB0

W6 W5 W4 W3 W2 W1 W0

Res. rs rw rw rw rw rw rw rw rw rw

Loading...

Loading...