Debug support (DBG) RM0008

666/690

The address of the 32-bits AHP-AP resisters are 6-bits wide (up to 64 words or 256 bytes)

and consists of:

f) Bits [8:4] = the bits[7:4] APBANKSEL of the DP SELECT register

g) Bits [3:2] = the 2 address bits of A(3:2) of the 35-bit packet request for SW-DP.

The AHB-AP of the Cortex-M3 includes 9 x 32-bits registers:

Refer to the Cortex-M3 r1p1 TRM for further details.

26.10 Core debug

Core debug is accessed through the core debug registers. Debug access to these registers

is by means of the Advanced High-performance Bus (AHB-AP) port. The processor can

access these registers directly over the internal Private Peripheral Bus (PPB).

It consists of 4 registers:

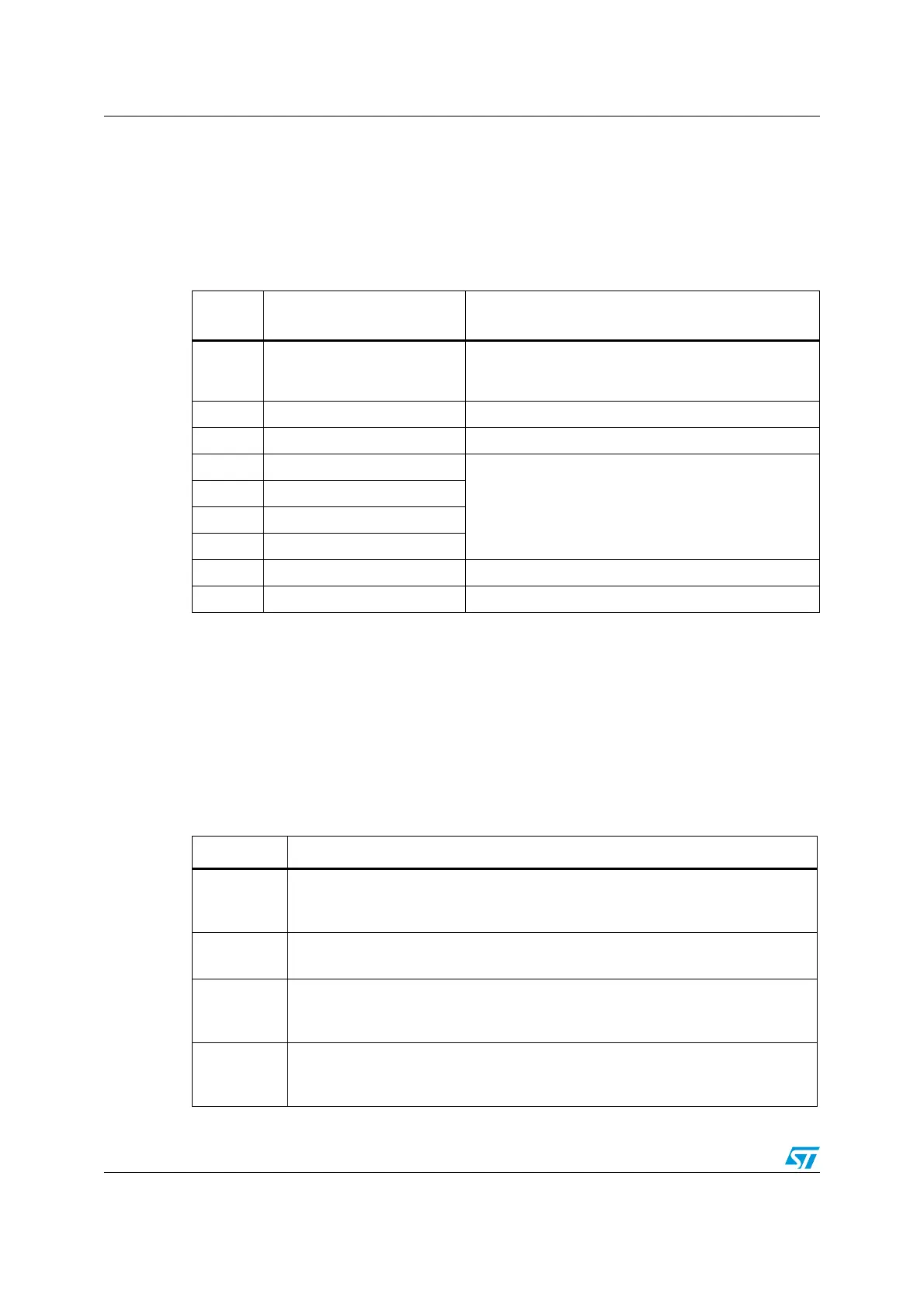

Table 166. Cortex-M3 AHB-AP registers

Address

offset

Register name Notes

0x00

AHB-AP Control and

Status Word

Configures and controls transfers through the AHB

interface (size, hprot, status on current transfer, address

increment type

0x04 AHB-AP Transfer Address

0x0C AHB-AP Data Read/Write

0x10 AHB-AP Banked Data 0

Directly maps the 4 aligned data words without rewriting

the Transfer Address Register.

0x14 AHB-AP Banked Data 1

0x18 AHB-AP Banked Data 2

0x1C AHB-AP Banked Data 3

0xF8 AHB-AP Debug ROM Address Base Address of the debug interface

0xFC AHB-AP ID Register

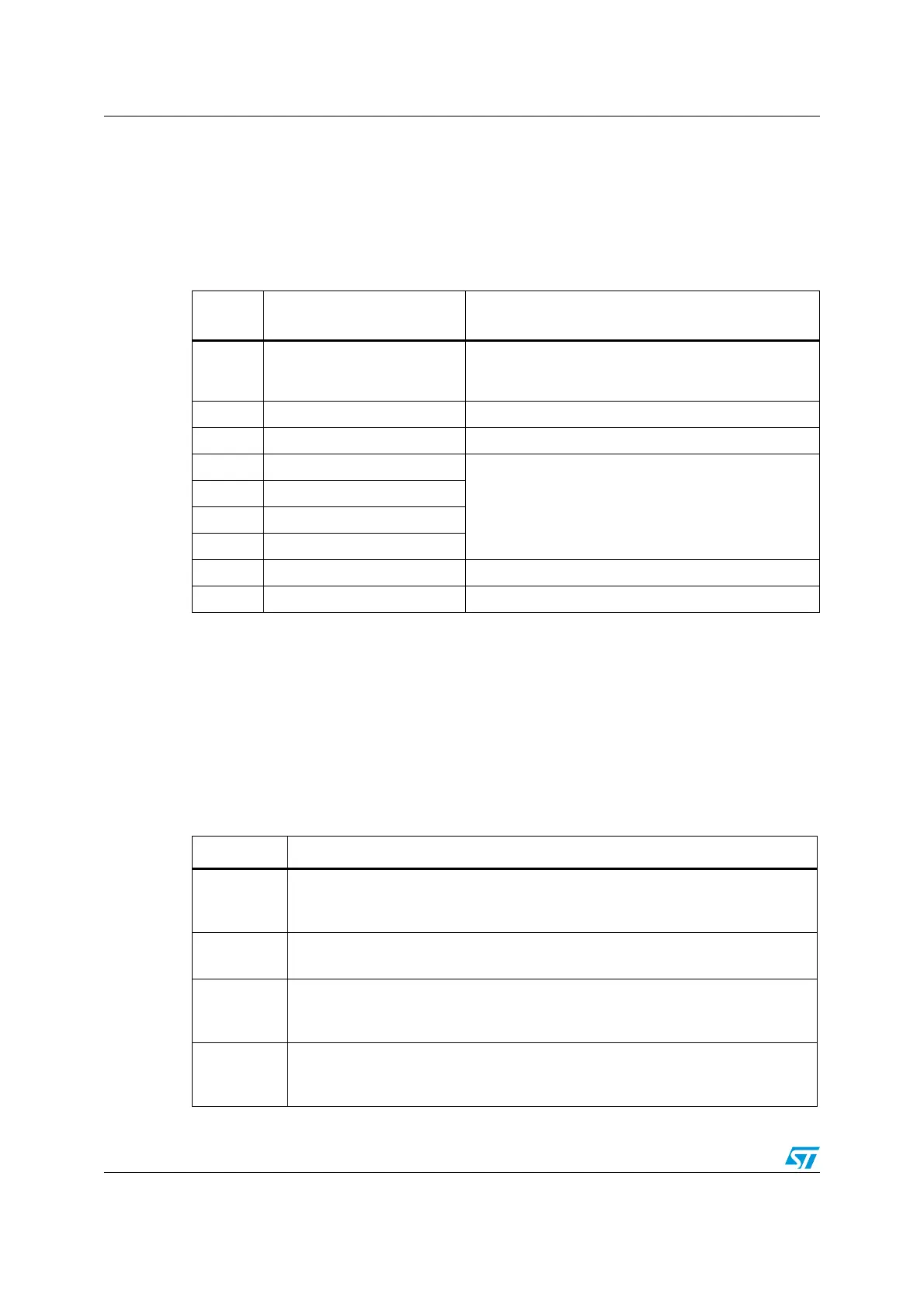

Table 167. Core debug registers

Register Description

DHCSR

The 32-bit Debug Halting Control and Status Register

This provides status information about the state of the processor enable core debug

halt and step the processor

DCRSR

The 17-bit Debug Core Register Selector Register:

This selects the processor register to transfer data to or from.

DCRDR

The 32-bit Debug Core Register Data Register:

This holds data for reading and writing registers to and from the processor selected

by the DCRSR (Selector) register.

DEMCR

The 32-bit Debug Exception and Monitor Control Register:

This provides Vector Catching and Debug Monitor Control. This register contains a

bit named TRCENA which enable the use of a TRACE.

Loading...

Loading...