RM0008 Debug support (DBG)

671/690

For the bxCAN, the user can choose to block the update of the receive register during a

breakpoint.

For the I

2

C, the user can choose to block the SMBUS timeout during a breakpoint.

26.15.3 Debug MCU configuration register

This register allows the configuration of the MCU under DEBUG. This concerns:

● Low-power mode support

● Timer and Watchdog counters support

● bxCAN communication support

● Trace pin assignment

This DBGMCU_CR is mapped on the External PPB bus at address 0xE004 2004

It is asynchronously reset by the PORESET (and not the system reset). It can be written by

the debugger under system reset.

If the debugger host does not support these features, it is still possible for the user software

to write to these registers.

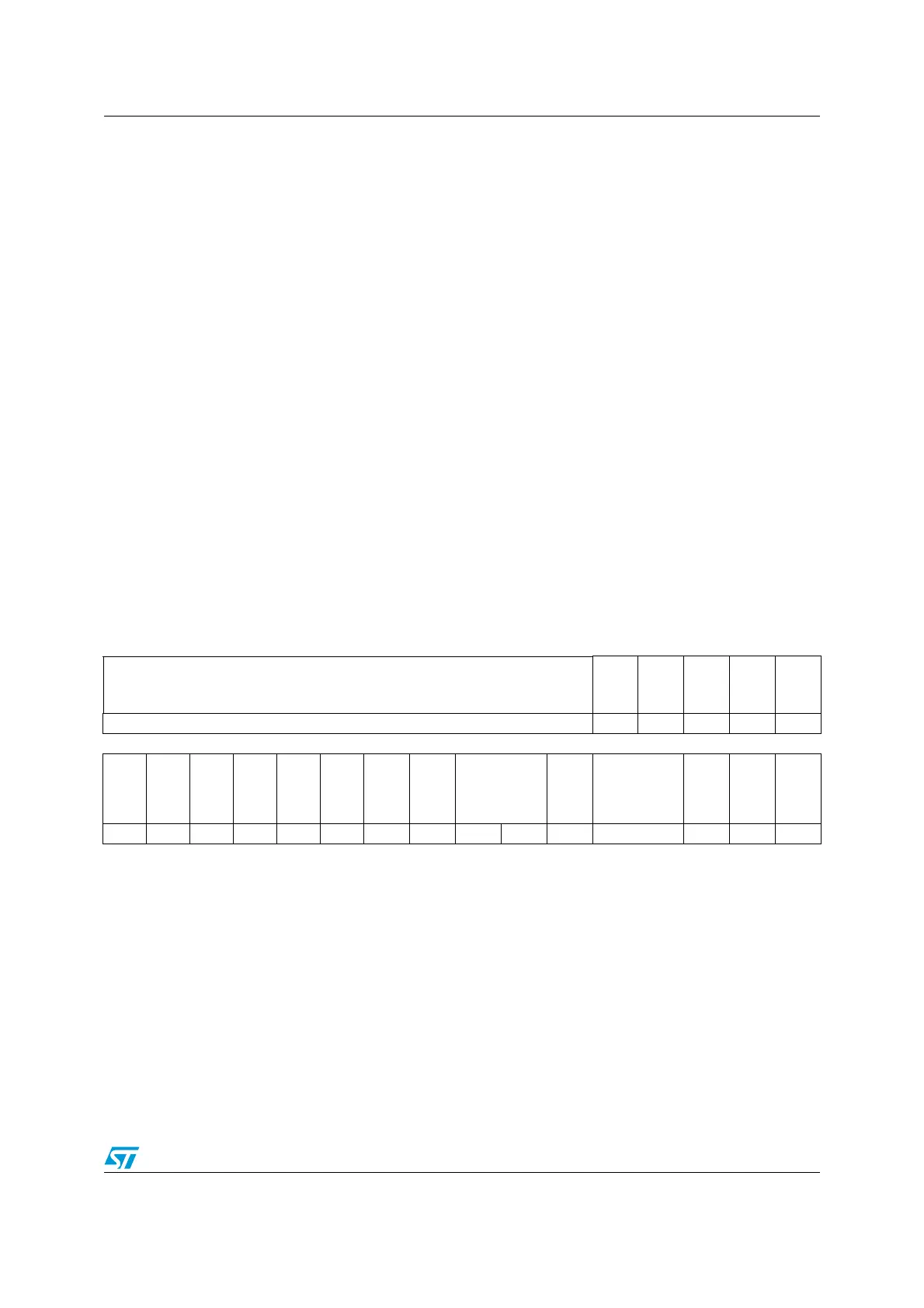

DBGMCU_CR

Address: 0xE0042004

Only 32-bit access supported

POR Reset: 0x00000000 (not reset by system reset)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

DBG_

TIM8_

STOP

DBG_

TIM7_

STOP

DBG_

TIM6_

STOP

DBG_

TIM5_

STOP

DBG_I2

C2_SM

BUS_TI

MEOUT

Res. rw rw rw rw rw

1514131211109876543210

DBG_I

2C1_S

MBUS

_TIME

OUT

DBG_

CAN_

STOP

DBG_

TIM4_

STOP

DBG_

TIM3_

STOP

DBG_

TIM2_

STOP

DBG_

TIM1_

STOP

DBG_

WWDG

_

STOP

DBG_

IWDG

STOP

TRACE_

MODE

[1:0]

TRACE

_

IOEN

Reserved

DBG_

STAND

BY

DBG_

STOP

DBG_

SLEEP

rw rw rw rw rw rw rw rw rw rw rw Res. rw rw rw

Bits 31:21 Reserved, must be kept cleared.

Bits 20:17 DBG_TIMx_STOP: TIMx counter stopped when core is halted (x=8..5)

0: The clock of the involved timer counter is fed even if the core is halted, and the outputs behave

normally.

1: The clock of the involved timer counter is stopped when the core is halted, and the outputs are

disabled (as if there were an emergency stop in response to a break event).

Bit 16 DBG_I2C2_SMBUS_TIMEOUT SMBUS timeout mode stopped when Core is halted

0: Same behavior as in normal mode.

1: The SMBUS timeout is frozen

Bit 15 DBG_I2C1_SMBUS_TIMEOUT SMBUS timeout mode stopped when Core is halted

0: Same behavior as in normal mode.

1: The SMBUS timeout is frozen.

Loading...

Loading...