Advanced-control timers (TIM1&TIM8) RM0008

214/690

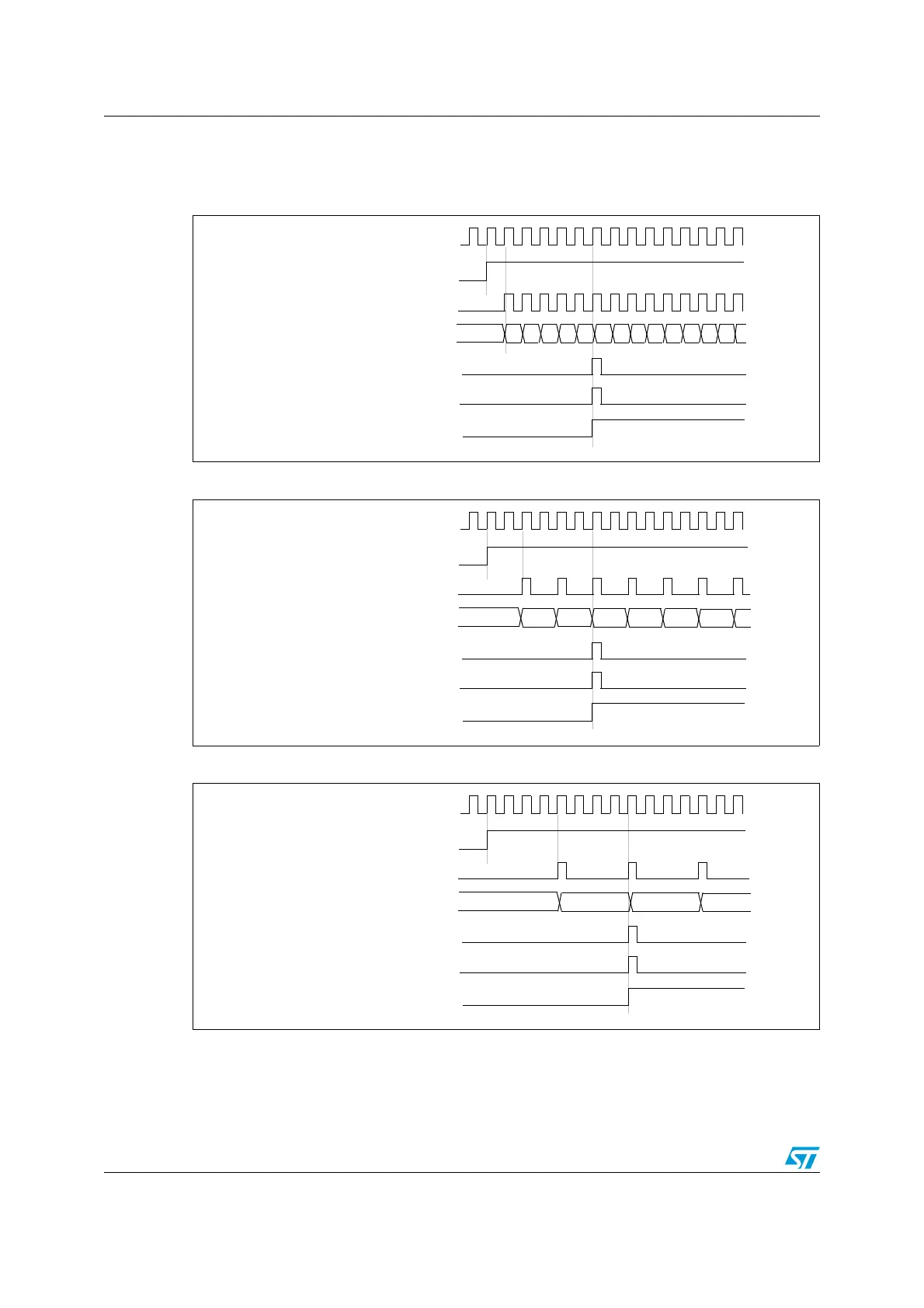

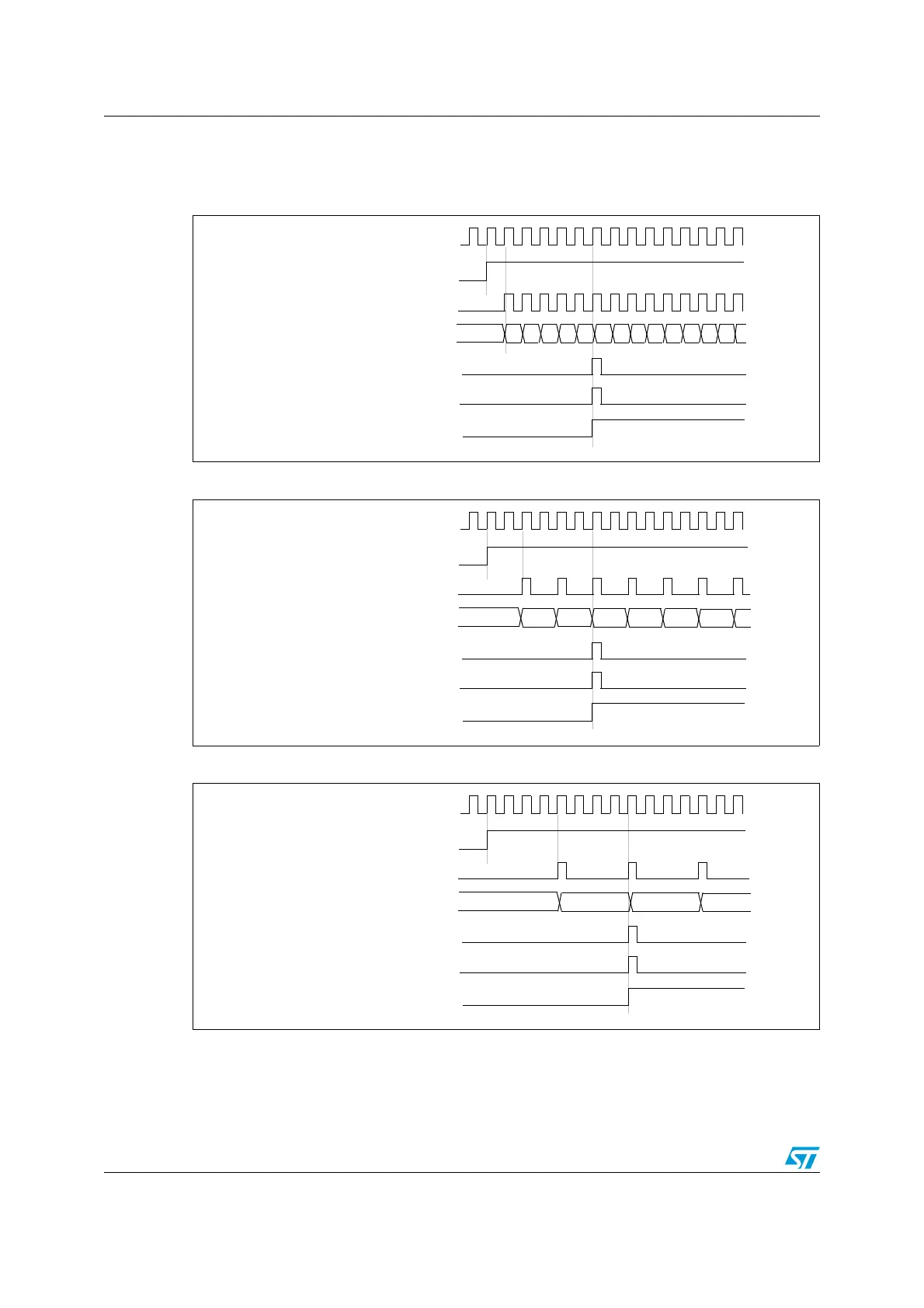

The following figures show some examples of the counter behavior for different clock

frequencies when TIMx_ARR=0x36.

Figure 56. Counter timing diagram, internal clock divided by 1

Figure 57. Counter timing diagram, internal clock divided by 2

Figure 58. Counter timing diagram, internal clock divided by 4

CK_PSC

36

CNT_EN

Timer clock = CK_CNT

Counter register

Update interrupt flag (UIF)

Counter underflow (cnt_udf)

Update event (UEV)

35 34 33 32 31 30 2F04 03 02 01 0005

CK_PSC

0001 0036 0035 0034 0033

CNT_EN

Timer clock = CK_CNT

Counter register

Update interrupt flag (UIF)

0002

0000

Counter underflow

Update event (UEV)

CK_PSC

0036 0035

CNT_EN

Timer clock = CK_CNT

Counter register

Update interrupt flag (UIF)

0001

0000

Counter underflow

Update event (UEV)

Loading...

Loading...