RM0008 Debug support (DBG)

659/690

Note: Important: Once Serial-Wire is selected using the dedicated ARM JTAG sequence, the

boundary scan TAP is automatically disabled (JTMS forced high).

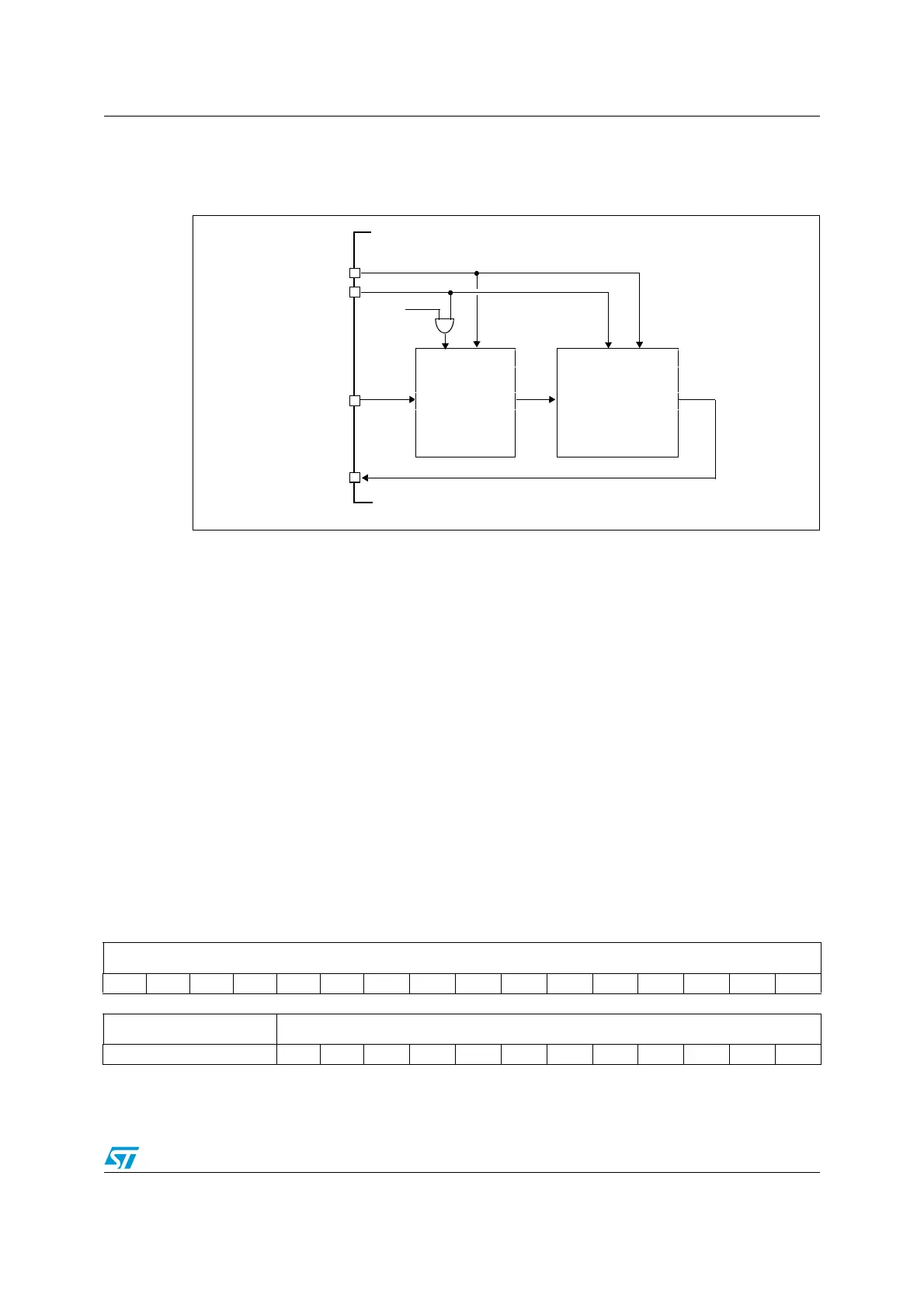

Figure 260. JTAG TAP connections

26.6 ID codes and locking mechanism

There are several ID codes inside the STM32F10xxx MCU. ST strongly recommends tools

designers to lock their debuggers using the MCU DEVICE ID code located in the external

PPB memory map at address 0xE0042000.

26.6.1 MCU device ID code

The STM32F10xxx MCU integrates an MCU ID code. This ID identifies the ST MCU part-

number and the die revision. It is part of the DBG_MCU component and is mapped on the

external PPB bus (see Section 26.15 on page 670). This code is accessible using the JTAG

debug port (4 to 5 pins) or the SW debug port (two pins) or by the user software. It is even

accessible while the MCU is under system reset.

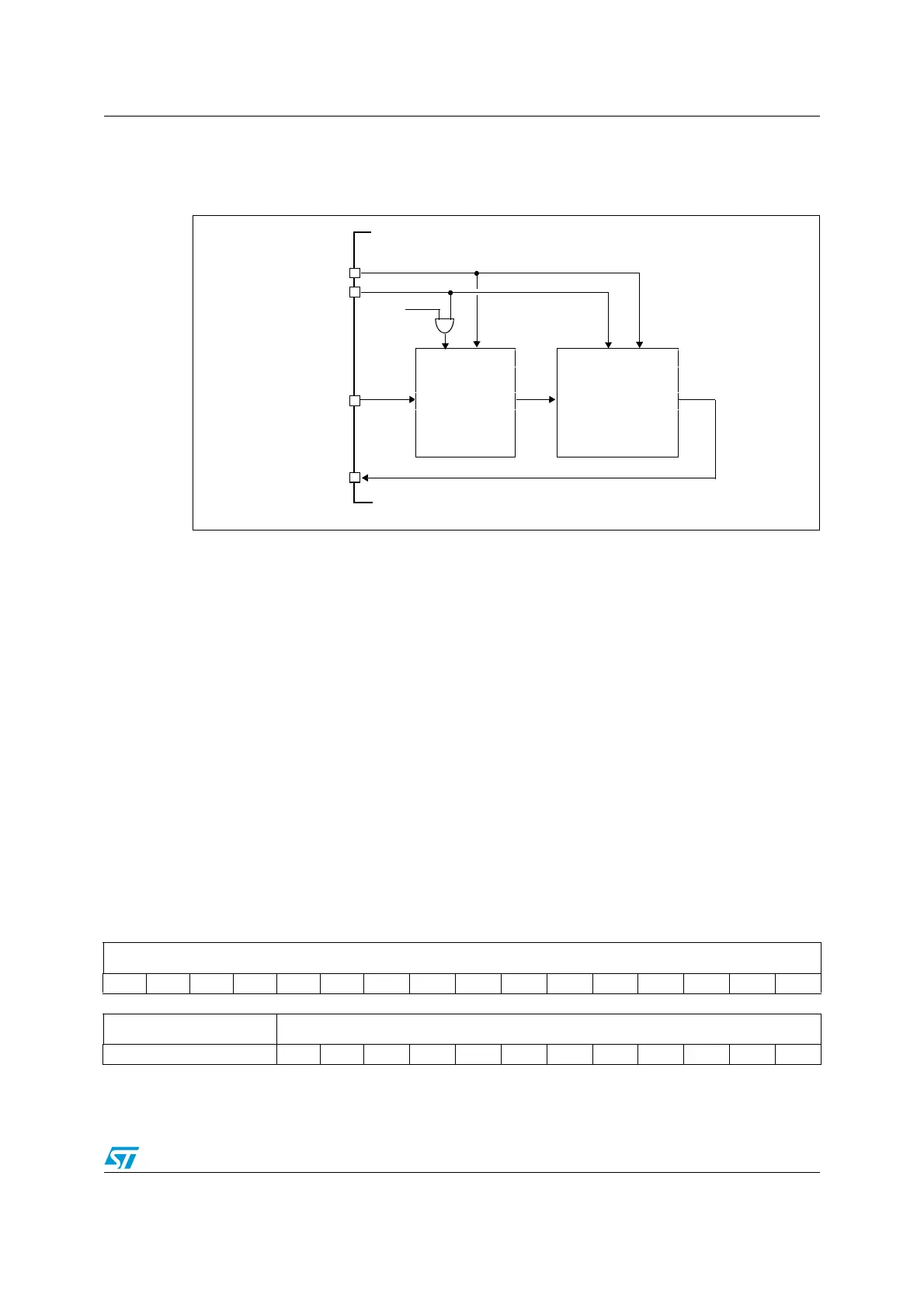

DBGMCU_IDCODE

Address: 0xE004 2000

Only 32-bits access supported. Read-only.

Boundary scan

TAP

JNTRST

Cortex-M3 TAP

JTMS

TMS nTRSTTMS nTRST

JTDI

JTDO

TDI TDO TDI TDO

SW-DP

STM32F10xxx

Selected

IR is 5-bit wide IR is 4-bit wide

ai14981

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

REV_ID

rrrrrrr r r r rrrrrr

1514131211109876543210

Reserved DEV_ID

Res. rrrrrrrrrrrr

Loading...

Loading...