SDIO interface (SDIO) RM0008

426/690

19.3.2 SDIO AHB Interface

The AHB interface generates the interrupt and DMA requests, and accesses the SDIO

adapter registers and the data FIFO. It consists of a data path, register decoder, and

interrupt/DMA logic.

SDIO Interrupts

The interrupt logic generates an interrupt request signal that is asserted when at least one

of the selected status flags is high. A mask register is provided to allow selection of the

conditions that will generate an interrupt. A status flag generates the interrupt request if a

corresponding mask flag is set.

SDIO/DMA Interface: procedure for data transfers between the SDIO and

memory

In the example shown, the transfer is from the SDIO host controller to an MMC (512 bytes

using CMD24 (WRITE_BLOCK). The SDIO FIFO is filled by data stored in a memory using

the DMA controller.

1. Do the card identification process

2. Increase the SDIO_CK frequency

3. Select the card by sending CMD7

4. Configure the DMA2 as follows:

a) Enable DMA2 controller and clear any pending interrupts

b) Program DMA2_Channel4 source address register with memory location base

address and DMA2_Channel4 destination address register with SDIO_FIFO

register address

c) Program DMA2_Channel4 control register (memory increment, not peripheral

increment, peripheral and source width is word size)

d) Enable DMA2_Channel4

5. Send CMD24 (WRITE_BLOCK) as follows:

a) Program the SDIO data length register (SDIO data timer register should be

already programmed before the card identification process)

b) Program the SDIO argument register with the address location of the card where

data is to be transferred

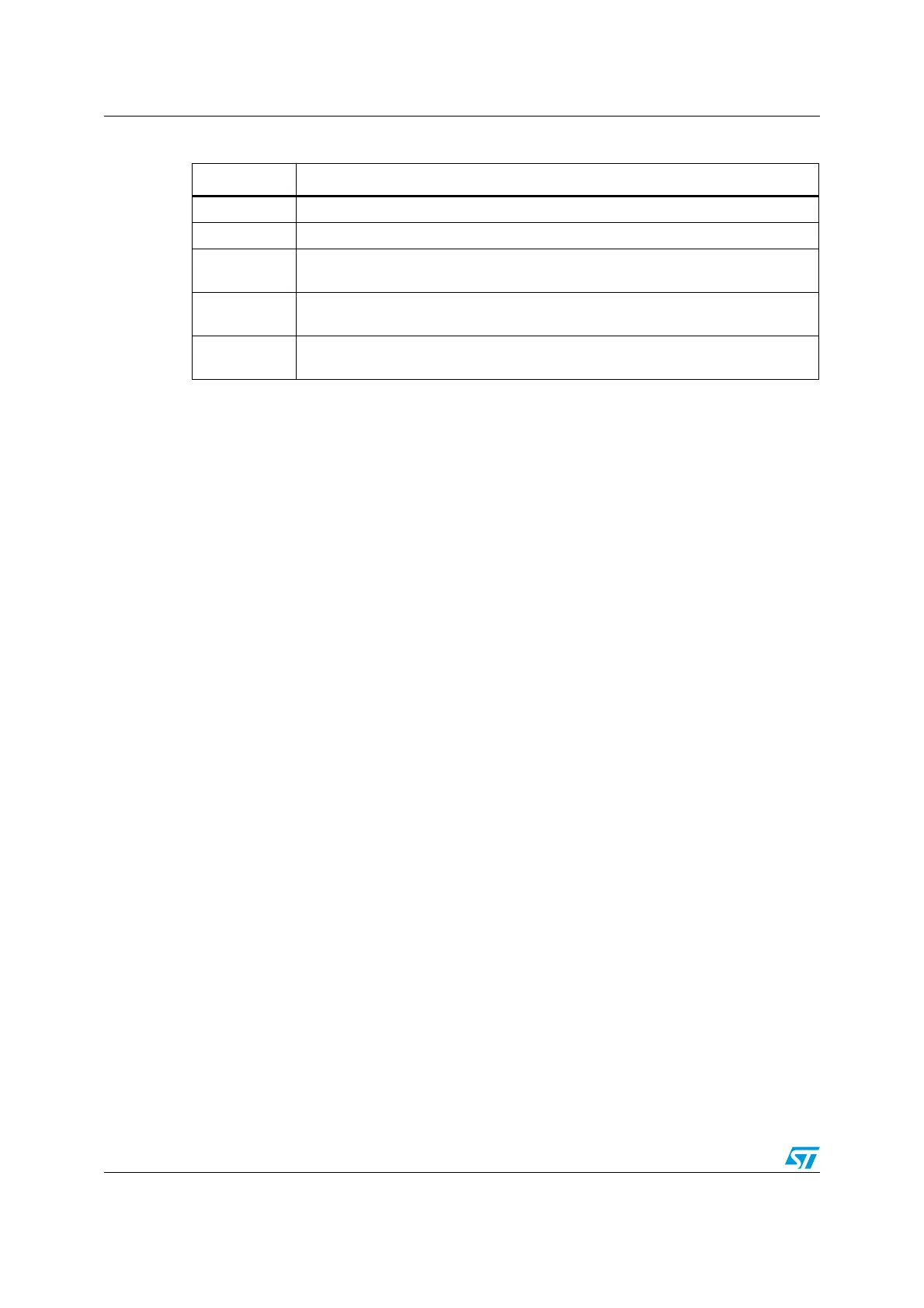

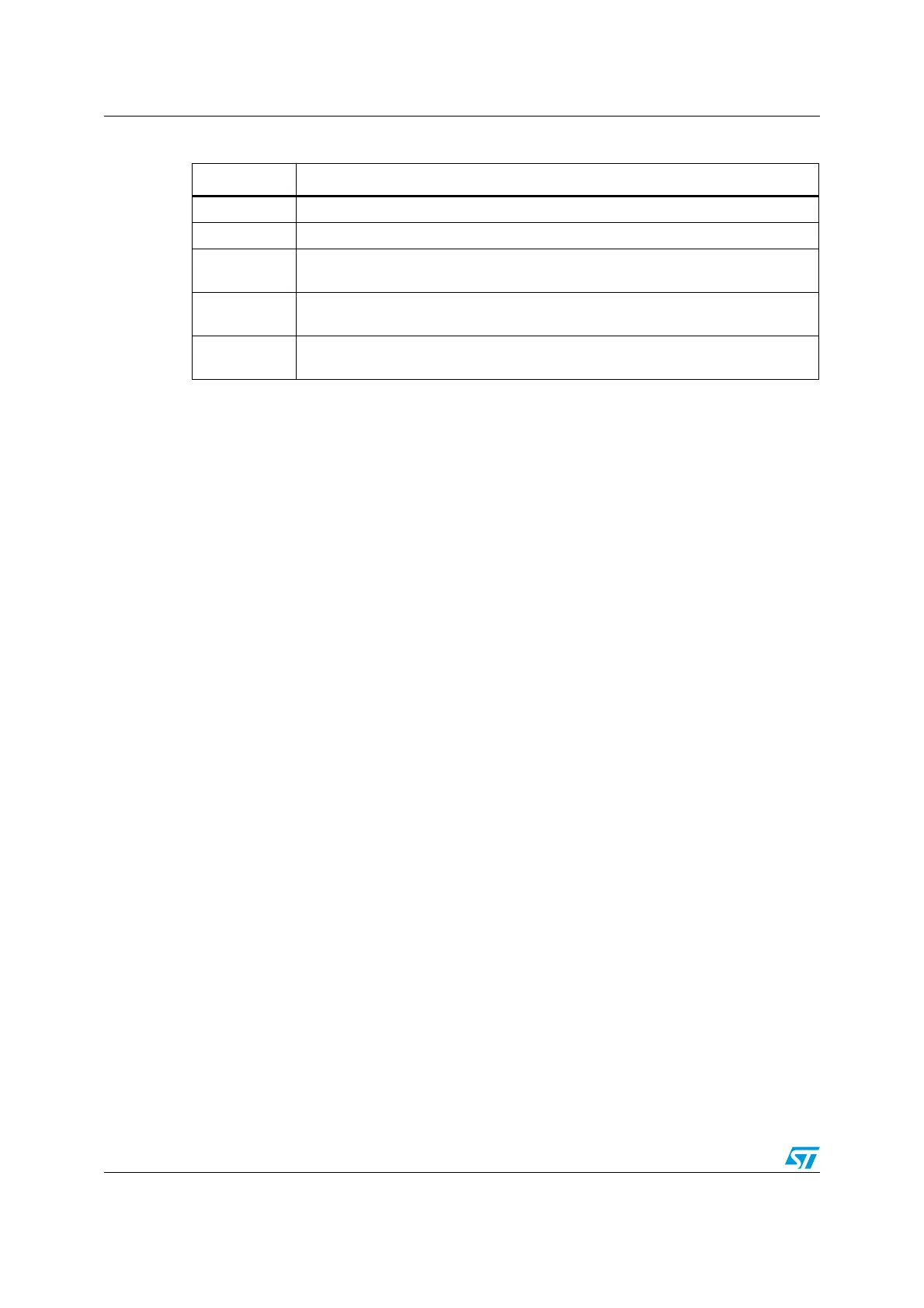

Table 108. Receive FIFO status flags

Flag Description

RXFIFOF Set to high when all 32 receive FIFO words contain valid data

RXFIFOE Set to high when the receive FIFO does not contain valid data.

RXFIFOHF

Set to high when 8 or more receive FIFO words contain valid data. This flag can be

used as a DMA request.

RXDAVL

Set to high when the receive FIFO is not empty. This flag is the inverse of the

RXFIFOE flag.

RXOVERR

Set to high when an overrun error occurs. This flag is cleared by writing to the SDIO

Clear register.

Loading...

Loading...