RM0008 Digital-to-analog converter (DAC)

205/690

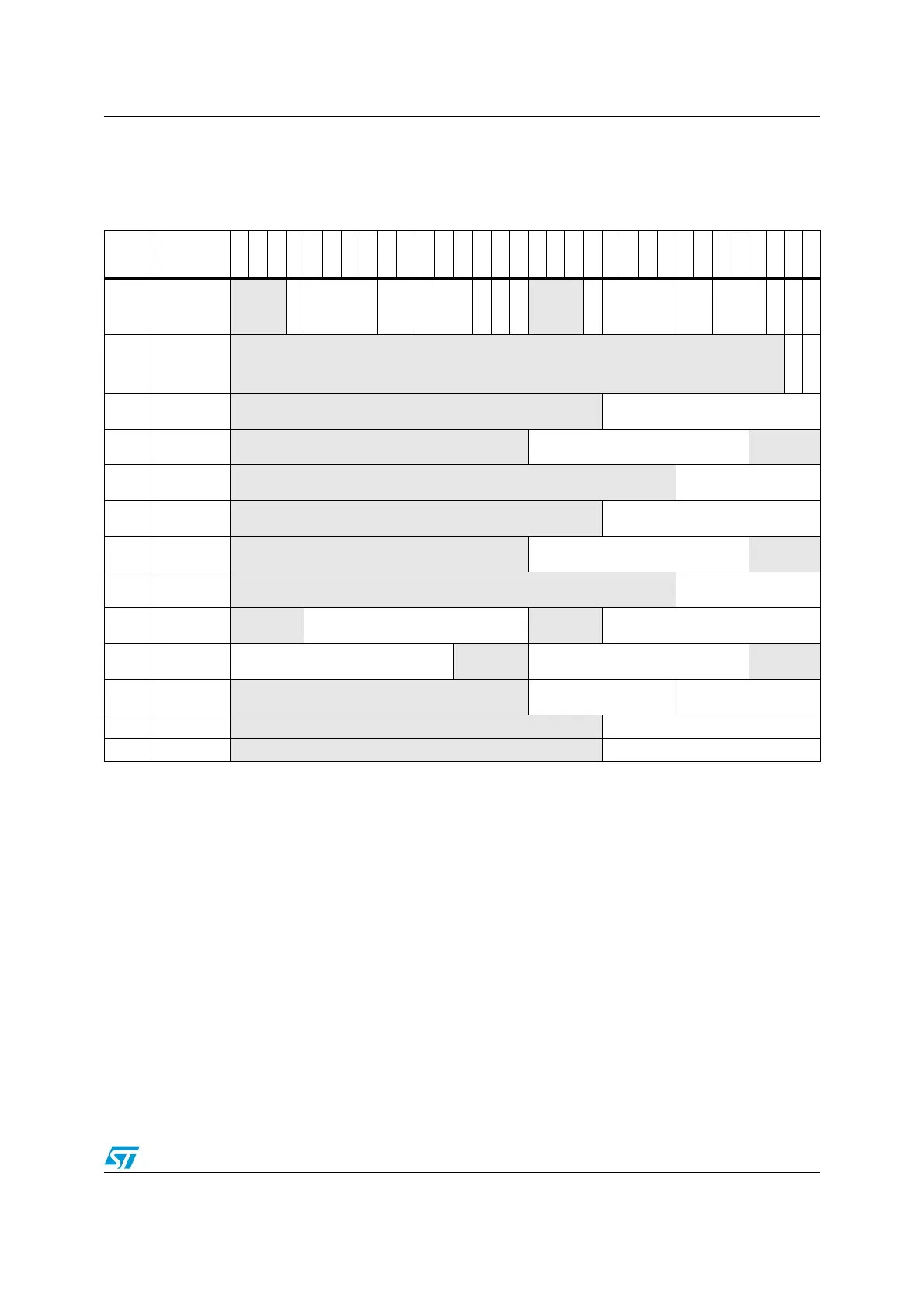

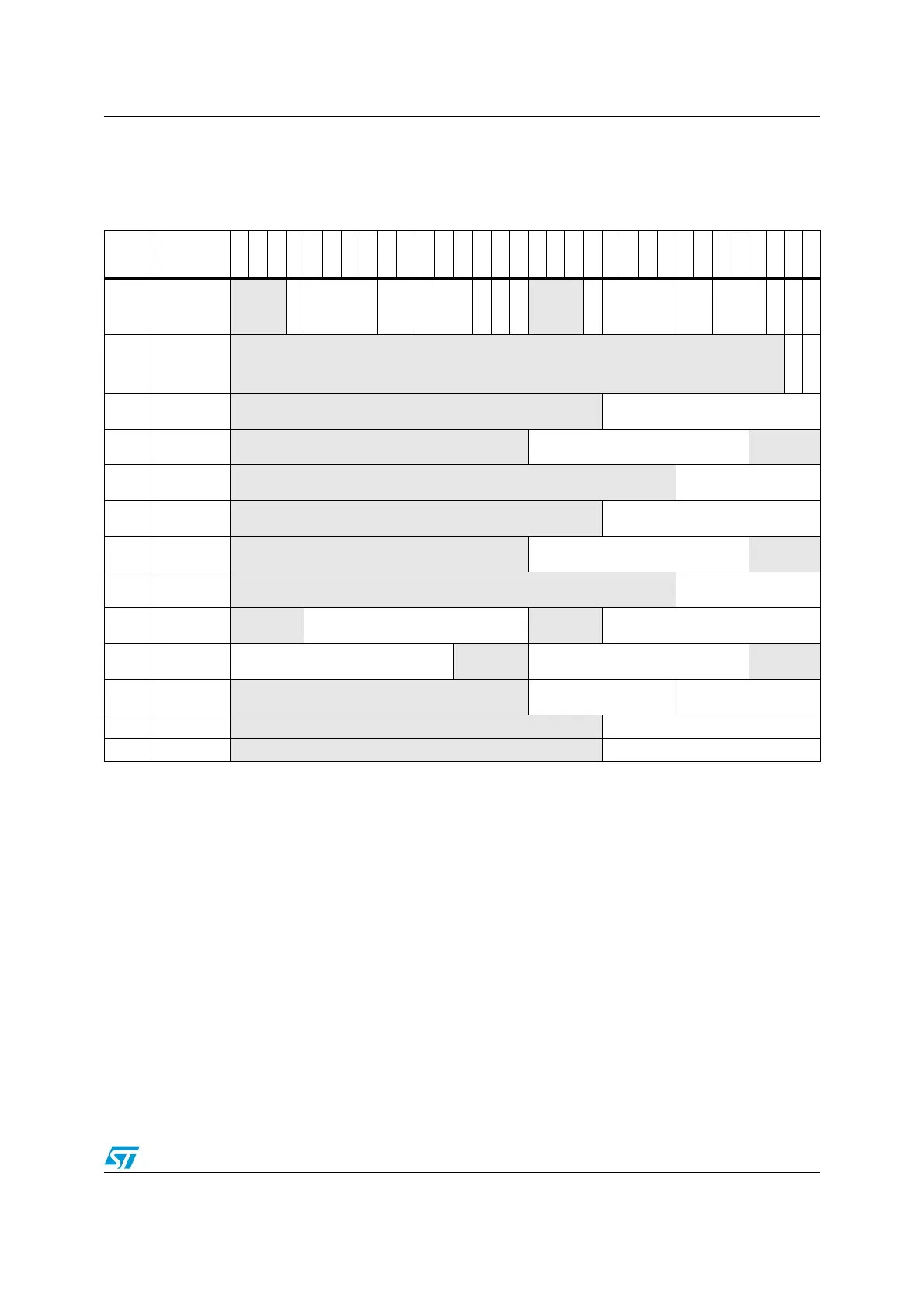

11.5.14 DAC register map

The following table summarizes the DAC registers.

Note: Refer to Table 1 on page 36 for the register boundary addresses.

Table 52. DAC Register map

Ad-

dress

offset

Name

31

0

0x00 DAC_CR

Reserved

DMAEN2

MAMP2[3:0]

WAV

E2[2:

0]

TSEL2[2:

0]

TEN2

BOFF2

EN2

Reserved

DMAEN1

MAMP1[3:0]

WAV

E1[2:

0]

TSEL1[2:

0]

TEN1

BOFF1

EN1

0x04

DAC_SWTRI

GR

Reserved

SWTRIG2

SWTRIG1

0x08

DAC_DHR12

R1

Reserved DACC1DHR[11:0]

0x0C

DAC_DHR12

L1

Reserved DACC1DHR[11:0] Reserved

0x10

DAC_DHR8R

1

Reserved DACC1DHR[7:0]

0x14

DAC_DHR12

R2

Reserved DACC2DHR[11:0]

0x18

DAC_DHR12

L2

Reserved DACC2DHR[11:0] Reserved

0x1C

DAC_DHR8R

2

Reserved DACC2DHR[7:0]

0x20

DAC_DHR12

RD

Reserved DACC2DHR[11:0] Reserved DACC1DHR[11:0]

0x24

DAC_DHR12

LD

DACC2DHR[11:0]

Reserved DACC1DHR[11:0] Reserved

0x28

DAC_DHR8R

D

Reserved DACC2DHR[7:0] DACC1DHR[7:0]

0x2C DAC_DOR1

Reserved DACC1DOR[11:0]

0x30 DAC_DOR2

Reserved DACC2DOR[11:0]

Loading...

Loading...