RM0008 Debug support (DBG)

655/690

26.2 Reference ARM documentation

● Cortex™-M3 r1p1 Technical Reference Manual (TRM)

● ARM Debug Interface V5

● ARM CoreSight Design Kit revision r1p0 Technical Reference Manual

26.3 SWJ debug port (serial wire and JTAG)

The STM32F10xxx core integrates the Serial Wire / JTAG Debug Port (SWJ-DP). It is an

ARM standard CoreSight debug port that combines a JTAG-DP (5-pin) interface and a SW-

DP (2-pin) interface.

● The JTAG Debug Port (JTAG-DP) provides a 5-pin standard JTAG interface to the AHP-

AP port.

● The Serial Wire Debug Port (SW-DP) provides a 2-pin (clock + data) interface to the

AHP-AP port.

In the SWJ-DP, the two JTAG pins of the SW-DP are multiplexed with some of the five JTAG

pins of the JTAG-DP.

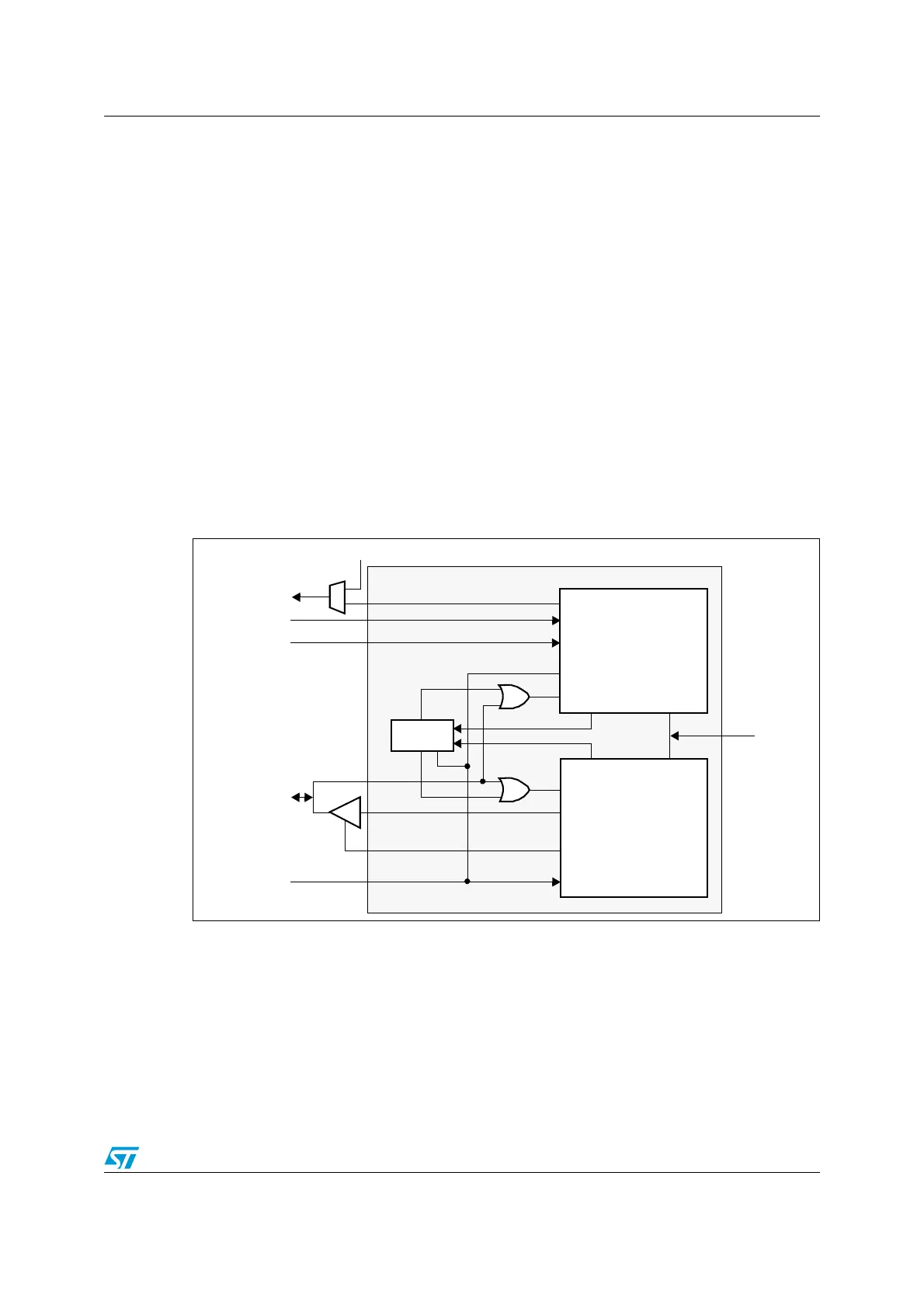

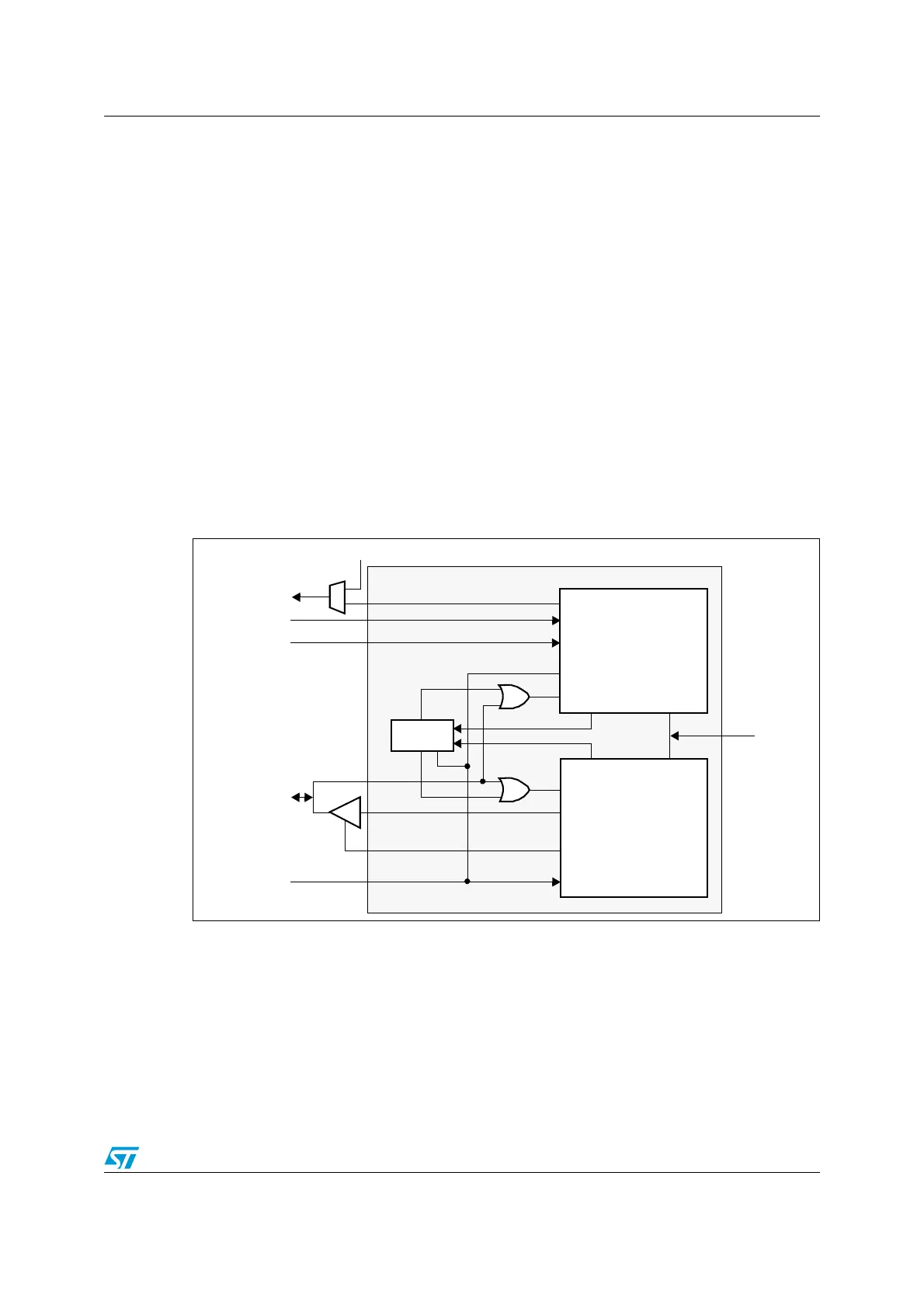

Figure 259. SWJ debug port

Figure 259 shows that the asynchronous TRACE output (TRACESWO) is multiplexed with

TDO. This means that the asynchronous trace can only be used with SW-DP, not JTAG-DP.

26.3.1 Mechanism to select the JTAG-DP or the SW-DP

By default, the JTAG-Debug Port is active.

If the debugger host wants to switch to the SW-DP, it must provide a dedicated JTAG

sequence on TMS/TCK (respectively mapped to SWDIO and SWCLK) which disables the

TRACESWO

JTDO

JTDI

JNTRST

nTRST

TDI

TDO

SWJ-DP

TDO

TDI

nTRST

TCK

TMS

nPOTRST

JTAG-DP

nPOTRST

From

power-on

reset

DBGRESETn

DBGDI

DBGDO

DBGDOEN

DBGCLK

SW-DP

SWCLKTCK

SWDOEN

SWDO

SWDITMS

SWD/JTAG

select

JTMS/SWDIO

JTCK/SWCLK

(asynchronous trace)

Loading...

Loading...