RM0008 Inter-integrated circuit (I

2

C) interface

605/690

23.6.7 Status register 2 (I2C_SR2)

Address offset: 0x18

Reset value:0x0000

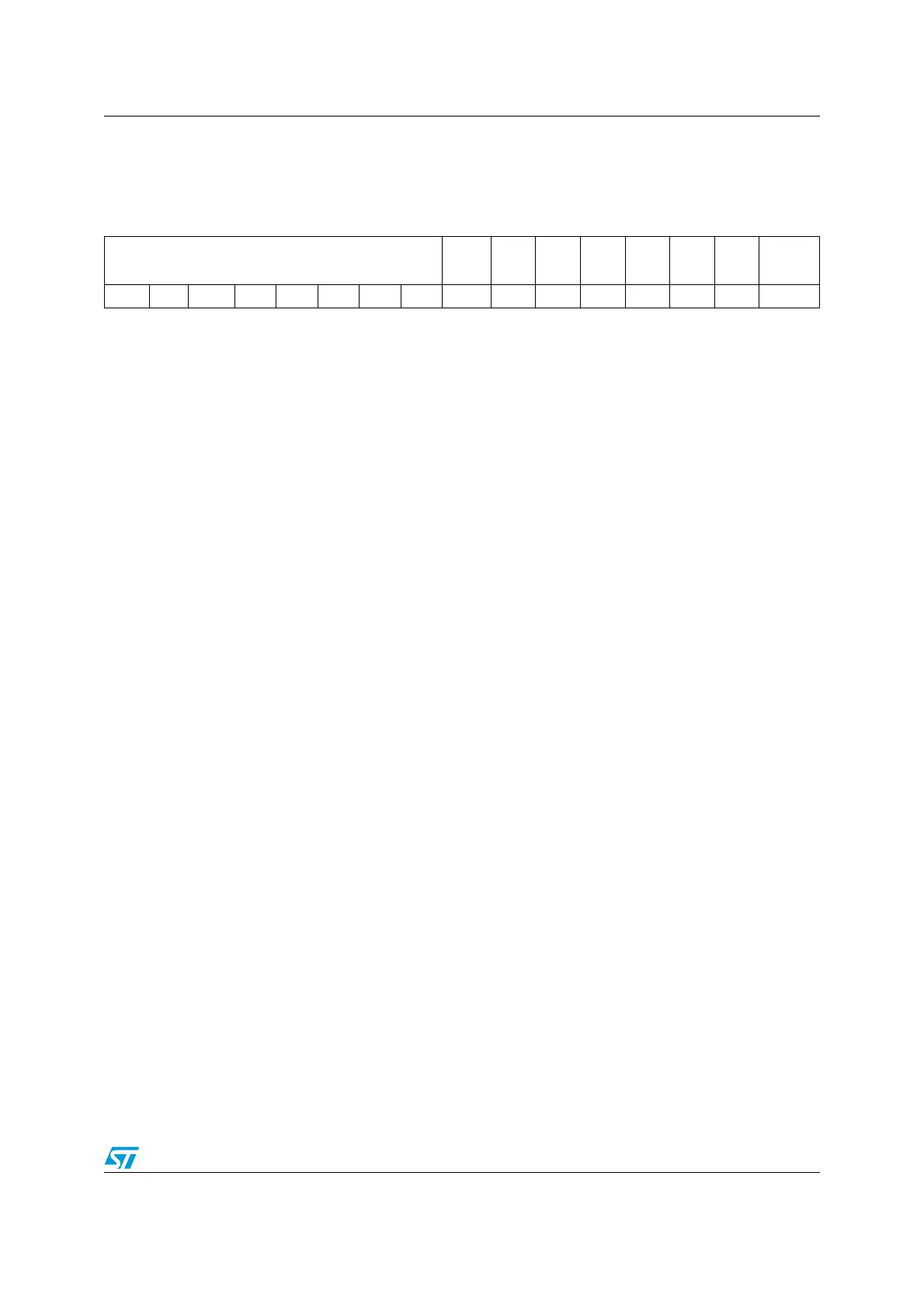

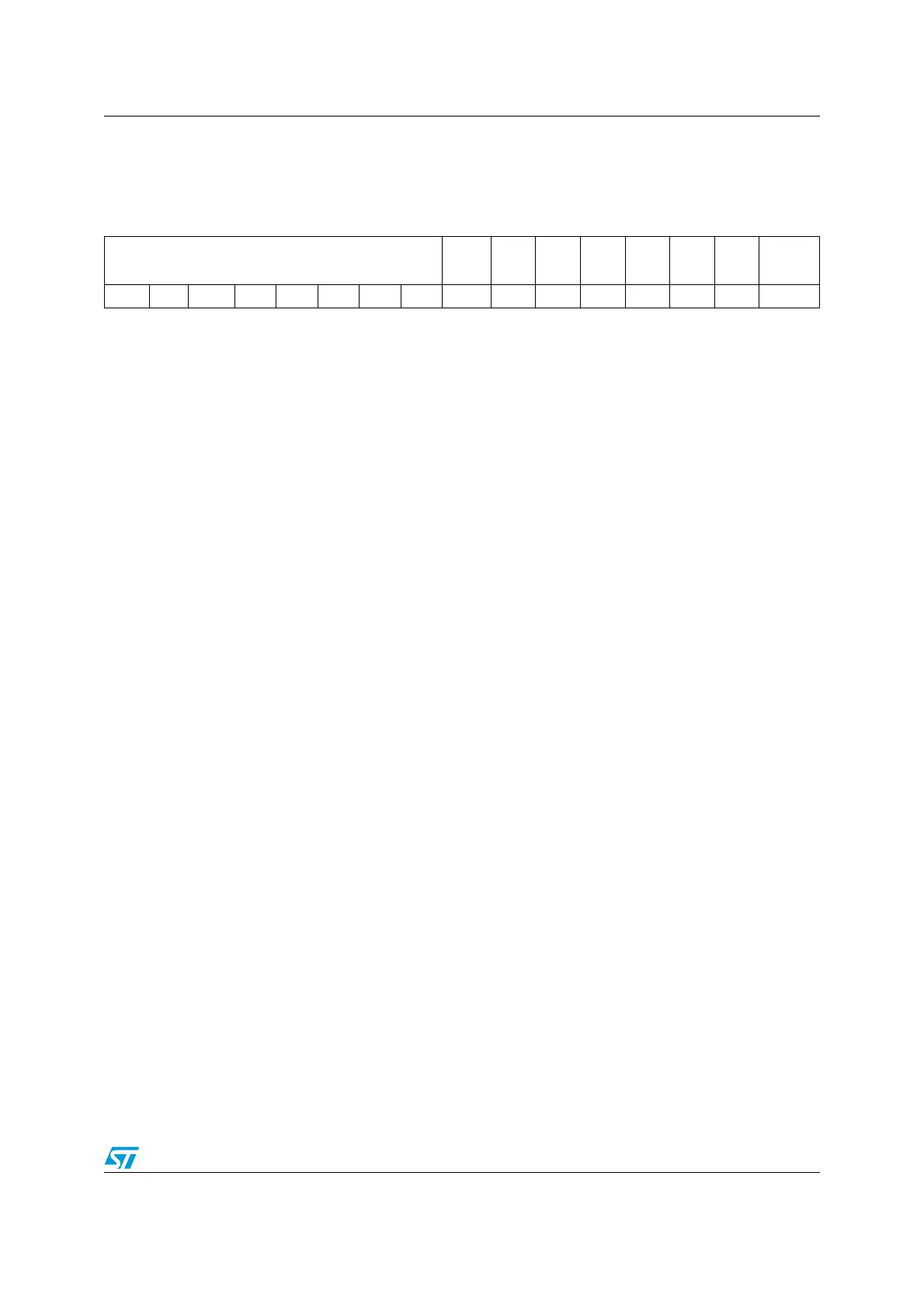

151413121110987 654321 0

PEC[7:0] DUALF

SMB

HOST

SMB

DEF

AULT

GEN

CALL

Res. TRA BUSY MSL

rr r rrrrr r r r r r r r

Bits 15:8 PEC[7:0] Packet Error Checking Register

This register contains the internal PEC when ENPEC=1.

Bit 7 DUALF: Dual Flag (Slave mode)

0: Received address matched with OAR1

1: Received address matched with OAR2

– Cleared by hardware after a Stop condition or repeated Start condition, or when PE=0.

Bit 6 SMBHOST: SMBus Host Header (Slave mode)

0: No SMBus Host address

1: SMBus Host address received when SMBTYPE=1 and ENARP=1.

– Cleared by hardware after a Stop condition or repeated Start condition, or when PE=0.

Bit 5 SMBDEFAULT: SMBus Device Default Address (Slave mode)

0: No SMBus Device Default address

1: SMBus Device Default address received when ENARP=1

– Cleared by hardware after a Stop condition or repeated Start condition, or when PE=0.

Bit 4 GENCALL: General Call Address (Slave mode)

0: No General Call

1: General Call Address received when ENGC=1

– Cleared by hardware after a Stop condition or repeated Start condition, or when PE=0.

Bit 3 Reserved, forced by hardware to 0.

Loading...

Loading...