RM0008 Inter-integrated circuit (I

2

C) interface

599/690

23.6.2 Control register 2 (I2C_CR2)

Address offset: 0x04

Reset value: 0x0000

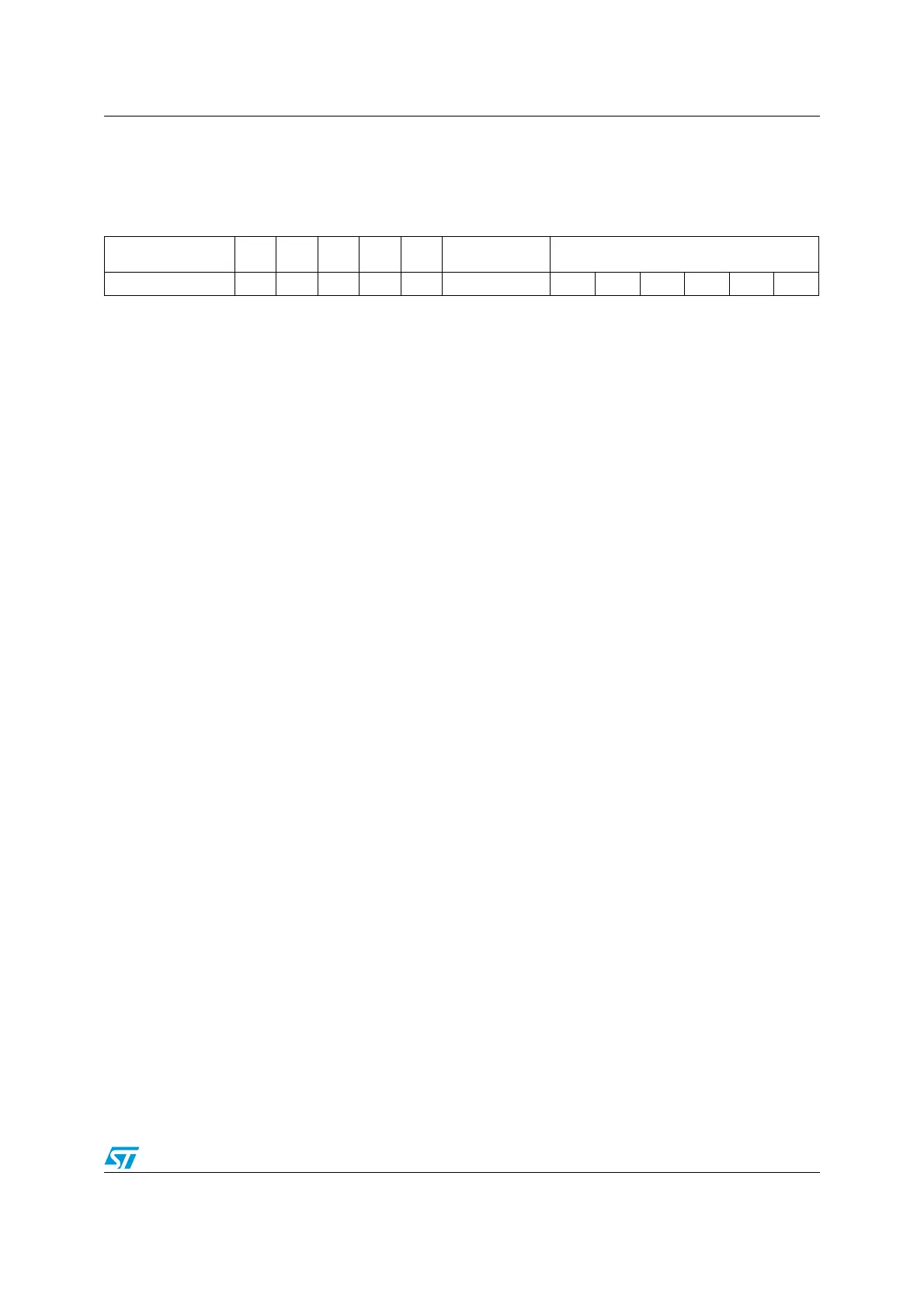

15141312111098 7 6543210

Reserved LAST

DMA

EN

ITBUF

EN

ITEVT

EN

ITER

REN

Reserved FREQ[5:0]

Res. rw rw rw rw rw Res. rw rw rw rw rw rw

Bits 15:13 Reserved, forced by hardware to 0.

Bit 12 LAST: DMA Last Transfer

0: Next DMA EOT is not the last transfer

1: Next DMA EOT is the last transfer

Note:

This bit is used in master receiver mode to permit the generation of a NACK on the last received data.

Bit 11 DMAEN: DMA Requests Enable

0: DMA requests disabled

1: DMA request enabled when TxE=1 or RxNE =1

Bit 10 ITBUFEN: Buffer Interrupt Enable

0: TxE = 1 or RxNE = 1 does not generate any interrupt.

1:TxE = 1 or RxNE = 1 generates Event Interrupt (whatever the state of DMAEN)

Bit 9 ITEVTEN: Event Interrupt Enable

0: Event interrupt disabled

1: Event interrupt enabled

This interrupt is generated when:

– SB = 1 (Master)

– ADDR = 1 (Master/Slave)

– ADD10= 1 (Master)

–STOPF = 1 (Slave)

– BTF = 1 with no TxE or RxNE event

– TxE event to 1 if ITBUFEN = 1

– RxNE event to 1if ITBUFEN = 1

Loading...

Loading...