RM0008 Flexible static memory controller (FSMC)

407/690

FIFO status and interrupt register 2..4 (FSMC_SR2..4)

Address offset: 0xA000 0000 + 0x44 + 0x20 * (x-1), x = 2..4

Reset value: 0x0000 0040

This register contains information about FIFO status and interrupt. The FSMC has a FIFO

that is used when writing to memories to store up to16 words of data from the AHB.

This is used to quickly write to the AHB and free it for transactions to peripherals other than

the FSMC, while the FSMC is draining its FIFO into the memory. This register has one of its

bits that indicates the status of the FIFO, for ECC purposes.

The ECC is calculated while the data are written to the memory, so in order to read the

correct ECC the software must wait until the FIFO is empty.

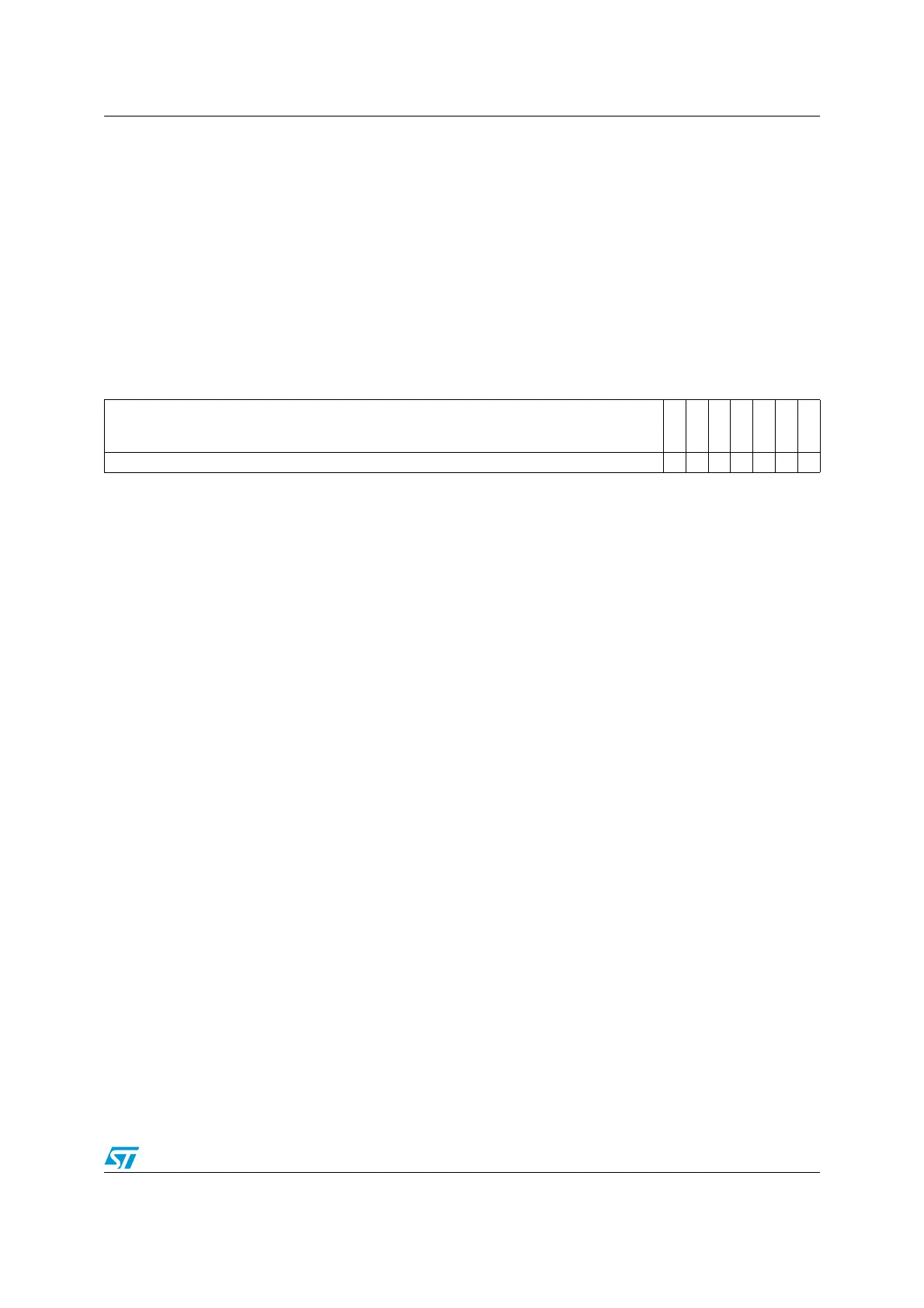

313029282726252423222120191817161514131211109876543210

Reserved

FEMPT

IFEN

ILEN

IREN

IFS

ILS

IRS

r r r/w r/w r/w r/w r/w r/w

Bit 6 FEMPT: FIFO empty.

Read-only bit that provides the status of the FIFO

0: FIFO not empty

1: FIFO empty

Bit 5 IFEN: Interrupt falling edge detection enable bit

0: Interrupt falling edge detection request disabled.

1: Interrupt falling edge detection request enabled.

Bit 4 ILEN: Interrupt high-level detection enable bit

0: Interrupt high-level detection request disabled.

1: Interrupt high-level detection request enabled.

Bit 3 IREN: Interrupt rising edge detection enable bit

0: Interrupt rising edge detection request disabled.

1: Interrupt rising edge detection request enabled.

Bit 2 IFS: Interrupt falling edge status

The flag is set by hardware and reset by software.

0: No interrupt falling edge occurred.

1: Interrupt falling edge occurred.

Bit 1 ILS: Interrupt high-level status

The flag is set by hardware and reset by software.

0: No Interrupt high-level occurred.

1: Interrupt high-level occurred.

Bit 0 IRS: Interrupt rising edge status

The flag is set by hardware and reset by software.

0: No interrupt rising edge occurred.

1: Interrupt rising edge occurred.

Loading...

Loading...