DocID024597 Rev 5 1515/1830

RM0351 Single Wire Protocol Master Interface (SWPMI)

1517

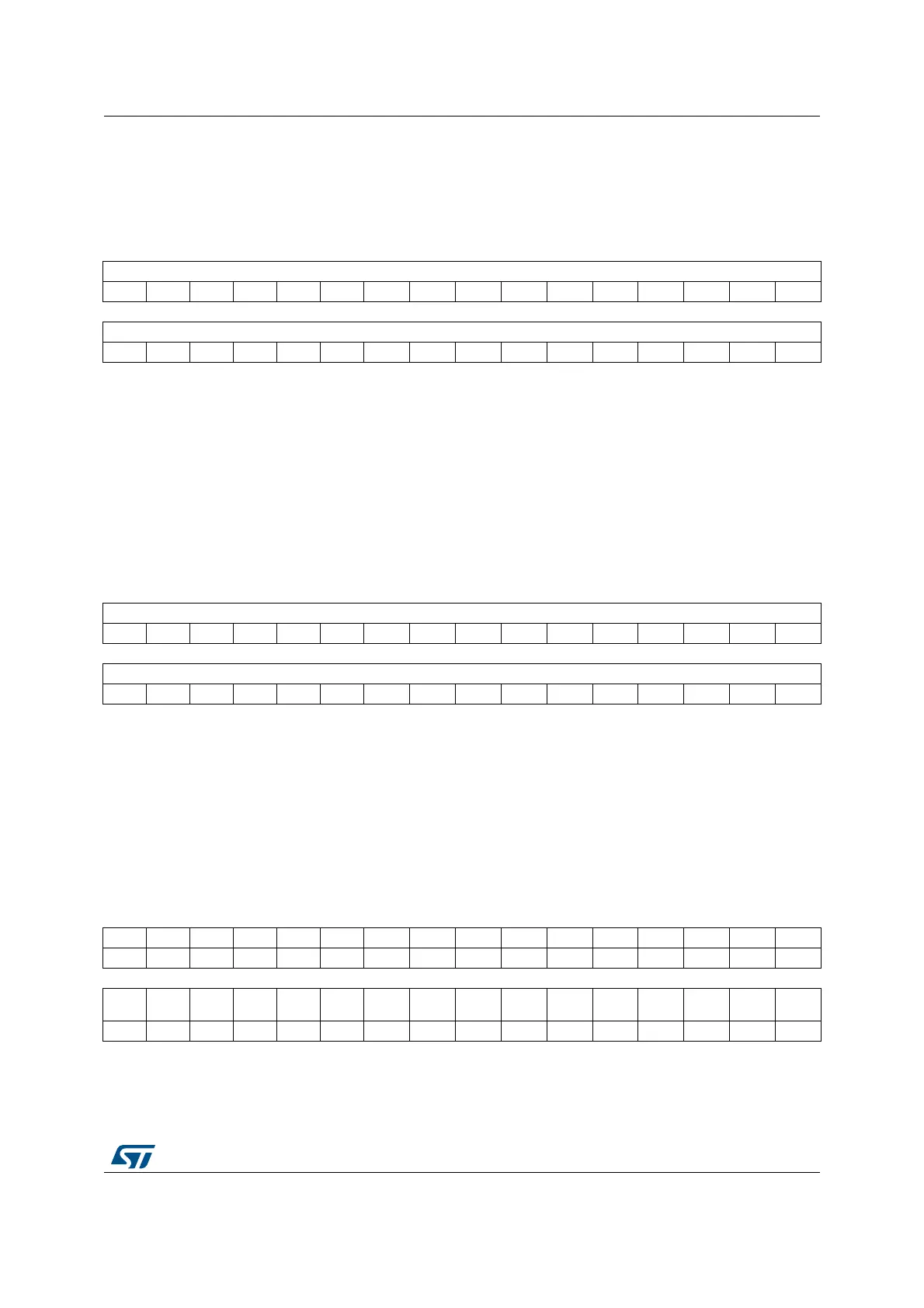

44.6.7 SWPMI Transmit data register (SWPMI_TDR)

Address offset: 0x1C

Reset value: 0x0000 0000

44.6.8 SWPMI Receive data register (SWPMI_RDR)

Address offset: 0x20

Reset value: 0x0000 0000

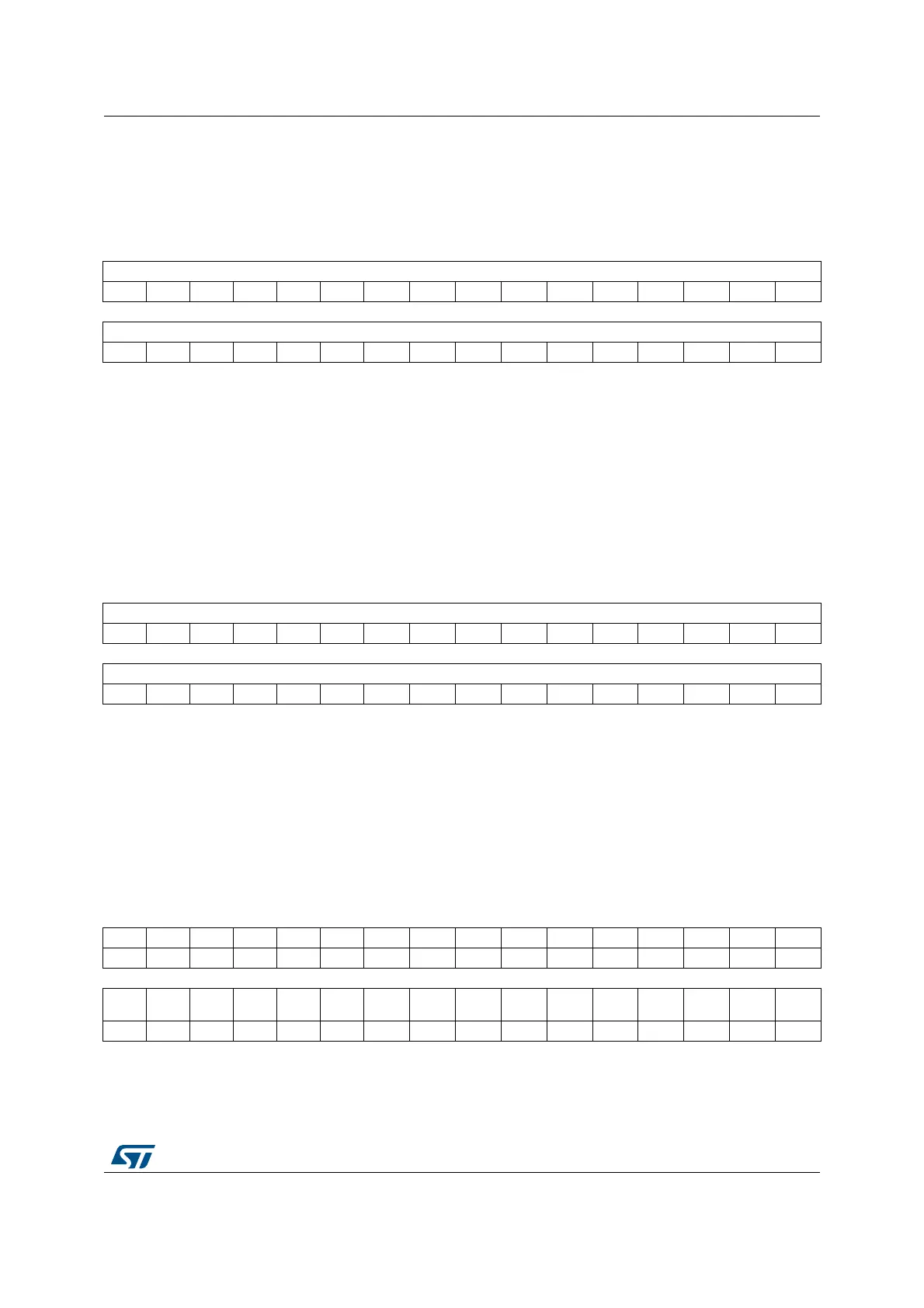

44.6.9 SWPMI Option register (SWPMI_OR)

Address offset: 0x24

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

TD[31:16]

wwwwww w w w w w w w w w w

1514131211109876543210

TD[15:0]

wwwwww w w w w w w w w w w

Bits 31:0 TD[31:0]: Transmit data

Contains the data to be transmitted.

Writing to this register triggers the SOF transmission or the next payload data transmission,

and clears the TXE flag.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

RD[31:16]

rrrrrr r r r r rrrrrr

1514131211109876543210

RD[15:0]

rrrrrr r r r r rrrrrr

Bits 31:0 RD[31:0]: received data

Contains the received data

Reading this register is clearing the RXNE flag.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

SWP_

CLASS

SWP_

TBYP

rw rw

Loading...

Loading...