DocID024597 Rev 5 1529/1830

RM0351 SD/SDIO/MMC card host interface (SDMMC)

1575

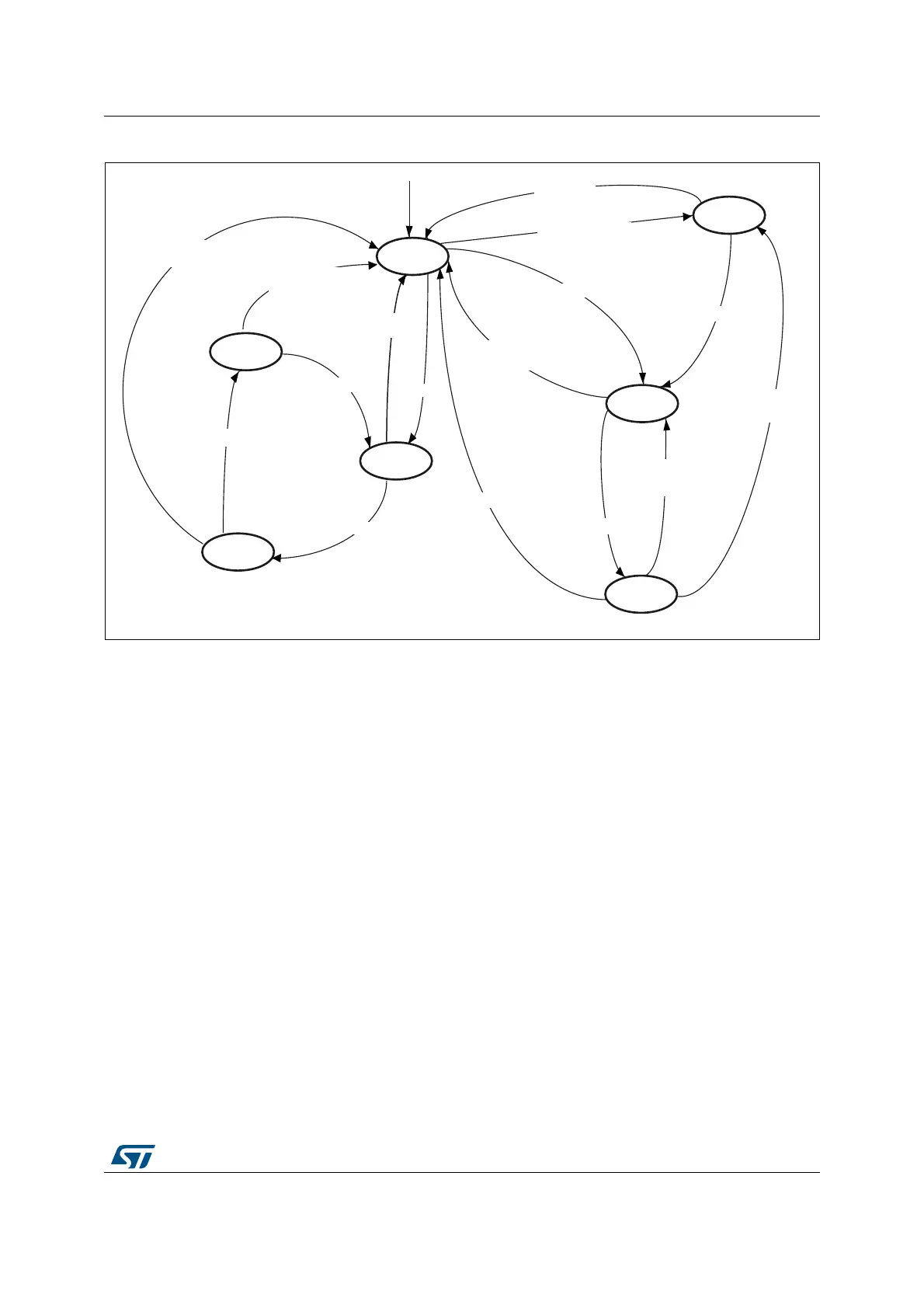

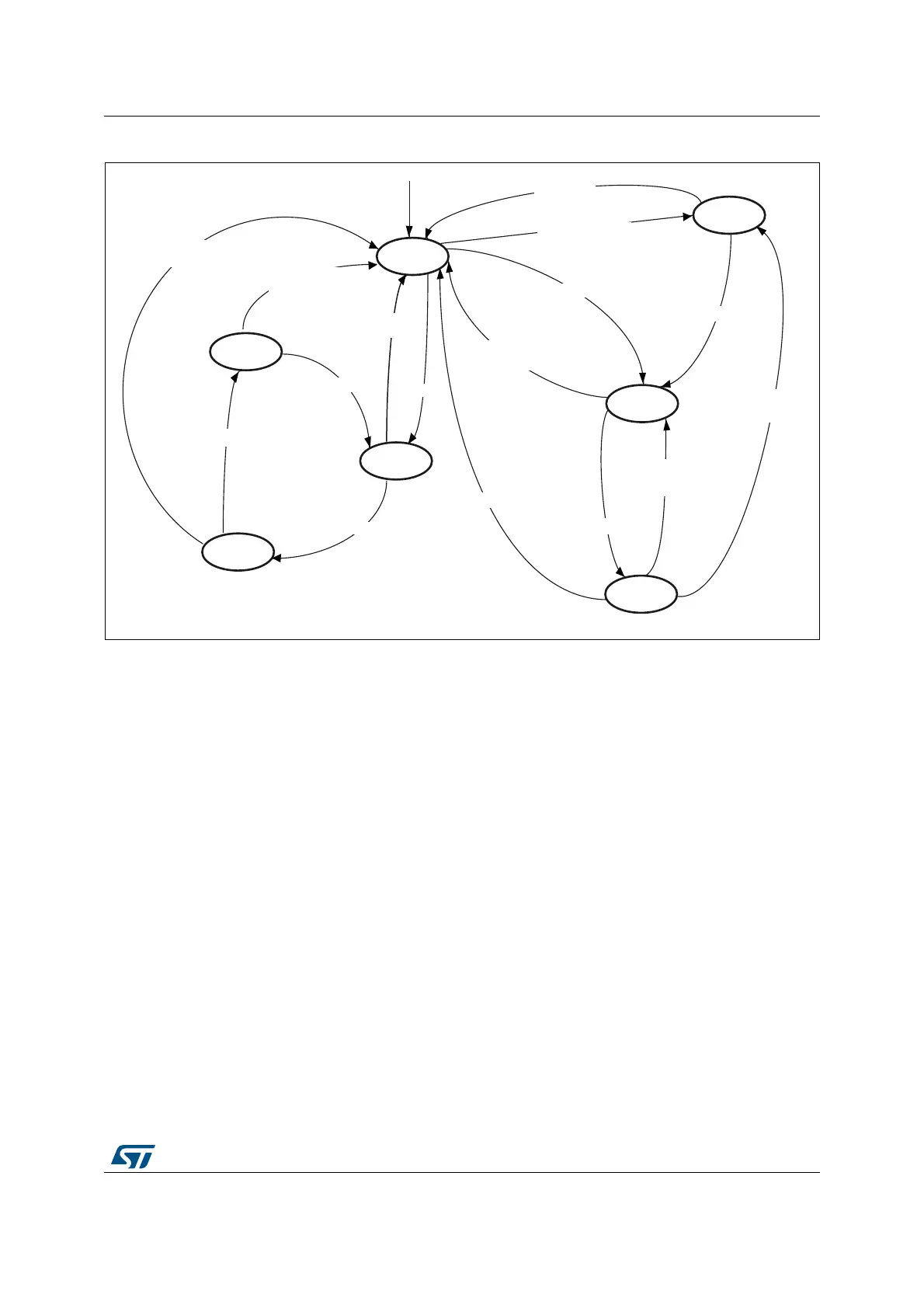

Figure 500. Data path state machine (DPSM)

• Idle: the data path is inactive, and the SDMMC_D[7:0] outputs are in Hi-Z. When the

data control register is written and the enable bit is set, the DPSM loads the data

counter with a new value and, depending on the data direction bit, moves to either the

Wait_S or the Wait_R state.

• Wait_R: if the data counter equals zero, the DPSM moves to the Idle state when the

receive FIFO is empty. If the data counter is not zero, the DPSM waits for a start bit on

SDMMC_D. The DPSM moves to the Receive state if it receives a start bit before a

timeout, and loads the data block counter. If it reaches a timeout before it detects a

start bit, it moves to the Idle state and sets the timeout status flag.

• Receive: serial data received from a card is packed in bytes and written to the data

FIFO. Depending on the transfer mode bit in the data control register, the data transfer

mode can be either block or stream:

– In block mode, when the data block counter reaches zero, the DPSM waits until it

receives the CRC code. If the received code matches the internally generated

CRC code, the DPSM moves to the Wait_R state. If not, the CRC fail status flag is

set and the DPSM moves to the Idle state.

– In stream mode, the DPSM receives data while the data counter is not zero. When

the counter is zero, the remaining data in the shift register is written to the data

FIFO, and the DPSM moves to the Wait_R state.

If a FIFO overrun error occurs, the DPSM sets the FIFO error flag and moves to the

Idle state:

• Wait_S: the DPSM moves to the Idle state if the data counter is zero. If not, it waits until

the data FIFO empty flag is deasserted, and moves to the Send state.

)DLE

"USY

3END

7AIT?2

2ECEIVE

%NDOFPACKET

$ISABLEDOR#2#FAIL

ORTIMEOUT

.OTBUSY

$ISABLEDOR

ENDOFDATA

$ATAREADY

%NDOFPACKETOR

ENDOFDATAOR

&)&/OVERRUN

%NABLEANDNOTSEND

$ISABLEDOR

2X&)&/EMPTYORTIMEOUTOR

STARTBITERROR

$ISABLEDOR&)&/UNDERRUNOR

ENDOFDATAOR#2#FAIL

AIB

7AIT?3

3TARTBIT

/NRESET

$ISABLEDOR#2#FAIL

%NABLEANDSEND

$03-DISABLED

2EAD7AIT

$03-ENABLEDAND

2EAD7AIT3TARTED

AND3$)/MODEENABLED

2EAD7AIT3TOP

$ATARECEIVEDAND

2EAD7AIT3TARTEDAND

3$)/MODEENABLED

Loading...

Loading...