Reset and clock control (RCC) RM0351

256/1830 DocID024597 Rev 5

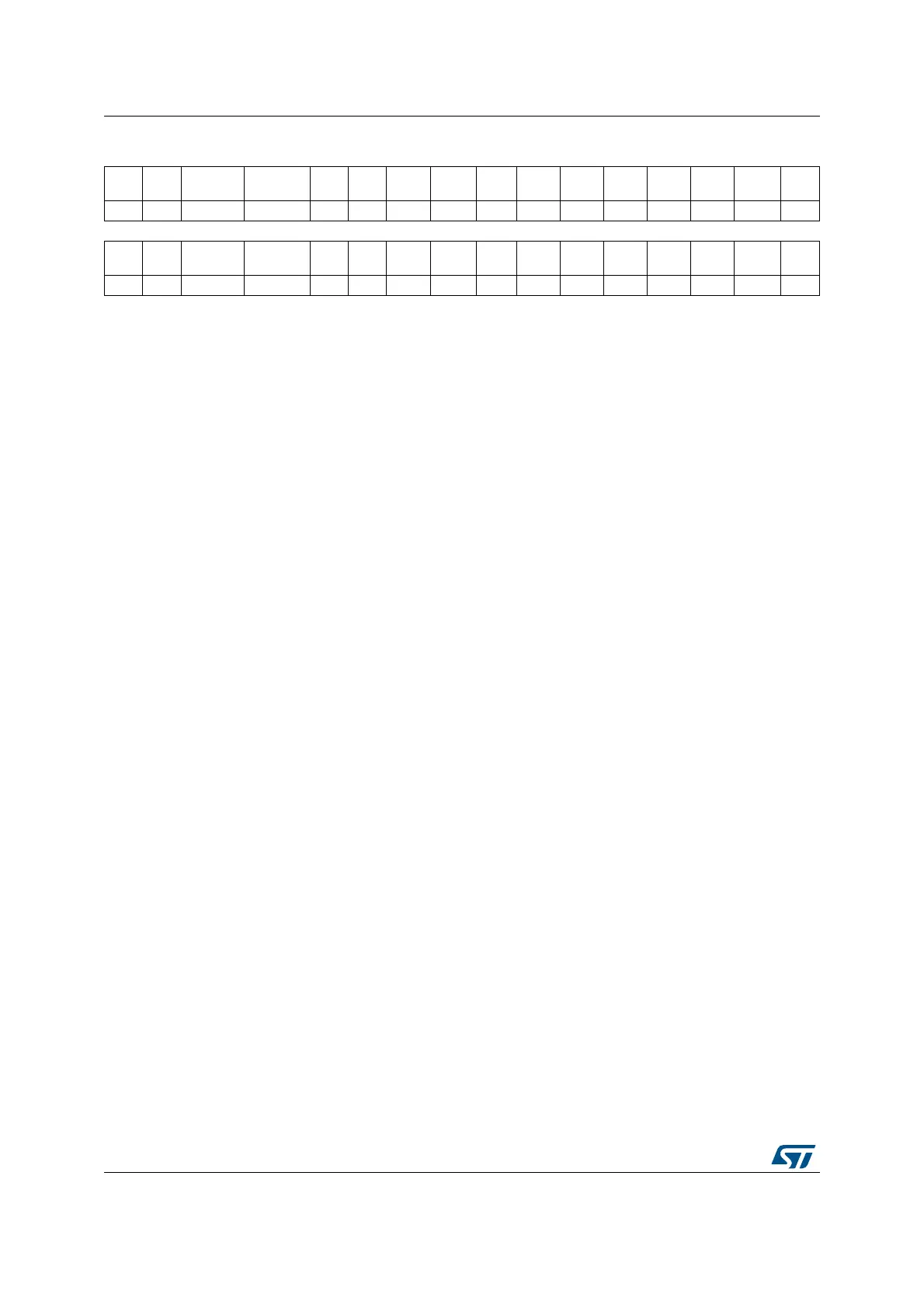

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

DMA2D

SMEN

TSC

SMEN

rw rw

1514 13 12 11109876543210

Res. Res. Res. CRCSMEN Res. Res.

SRAM1

SMEN

FLASH

SMEN

Res. Res. Res. Res. Res. Res.

DMA2

SMEN

DMA1

SMEN

rw rw rw rw rw

Bits 31:18 Reserved, must be kept at reset value.

Bit 17 DMA2DSMEN: DMA2D clock enable during Sleep and Stop modes (This bit is reserved for

STM32L475xx/476xx/486xx devices)

Set and cleared by software

0: DMA2D clocks disabled by the clock gating

(1)

during Sleep and Stop modes

1: DMA2D clocks enabled by the clock gating

(1)

during Sleep and Stop modes

Bit 16 TSCSMEN: Touch Sensing Controller clocks enable during Sleep and Stop modes

Set and cleared by software.

0: TSC clocks disabled by the clock gating

(1)

during Sleep and Stop modes

1: TSC clocks enabled by the clock gating

(1)

during Sleep and Stop modes

Bits 15:13 Reserved, must be kept at reset value.

Bit 12 CRCSMEN: CRC clocks enable during Sleep and Stop modes

Set and cleared by software.

0: CRC clocks disabled by the clock gating

(1)

during Sleep and Stop modes

1: CRC clocks enabled by the clock gating

(1)

during Sleep and Stop modes

Bits 11:10 Reserved, must be kept at reset value.

Bit 9 SRAM1SMEN: SRAM1 interface clocks enable during Sleep and Stop modes

Set and cleared by software.

0: SRAM1 interface clocks disabled by the clock gating

(1)

during Sleep and Stop modes

1: SRAM1 interface clocks enabled by the clock gating

(1)

during Sleep and Stop modes

Bit 8 FLASHSMEN: Flash memory interface clocks enable during Sleep and Stop modes

Set and cleared by software.

0: Flash memory interface clocks disabled by the clock gating

(1)

during Sleep and Stop

modes

1: Flash memory interface clocks enabled by the clock gating

(1)

during Sleep and Stop

modes

Bits 7:2 Reserved, must be kept at reset value.

Bit 1 DMA2SMEN: DMA2 clocks enable during Sleep and Stop modes

Set and cleared by software during Sleep mode.

0: DMA2 clocks disabled by the clock gating

(1)

during Sleep and Stop modes

1: DMA2 clocks enabled by the clock gating

(1)

during Sleep and Stop modes

Bit 0 DMA1SMEN: DMA1 clocks enable during Sleep and Stop modes

Set and cleared by software.

0: DMA1 clocks disabled by the clock gating

(1)

during Sleep and Stop modes

1: DMA1 clocks enabled by the clock gating

(1)

during Sleep and Stop modes

1. This register only configures the clock gating, not the clock source itself. Most of the peripherals are clocked by a single

clock (AHB or APB clock), which is always disabled in Stop mode. In this case setting the bit has no effect in Stop mode.

Loading...

Loading...