Chrom-Art Accelerator™ controller (DMA2D) RM0351

362/1830 DocID024597 Rev 5

The alpha channel can be:

• kept as it is (no modification),

• replaced by the ALPHA[7:0] value of DMA2D_FGPFCCR/DMA2D_BGPFCCR,

• or replaced by the original alpha value multiplied by the ALPHA[7:0] value of

DMA2D_FGPFCCR/DMA2D_BGPFCCR divided by 255.

Note: To support the alternate format, the incoming alpha value can be inverted setting the AI bit

of the DMA2D_FGPFCCR/DMA2D_BGPFCCR registers. This applies also to the Alpha

value stored in the DMA2D_FGPFCCR/DMA2D_BGPFCCR and in the CLUT.

The R and B fields can also be swapped setting the RBS bit of the

DMA2D_FGPFCCR/DMA2D_BGPFCCR registers. This applies also to the RGB order used

in the CLUT and in the DMA2D_FGCOLR/DMA2D_BGCOLR registers.

12.3.5 DMA2D foreground and background CLUT interface

The CLUT interface manages the CLUT memory access and the automatic loading of the

CLUT.

Three kinds of accesses are possible:

• CLUT read by the PFC during pixel format conversion operation

• CLUT accessed through the AHB slave port when the CPU is reading or writing data

into the CLUT

• CLUT written through the AHB master port when an automatic loading of the CLUT is

performed

The CLUT memory loading can be done in two different ways:

• Automatic loading

The following sequence should be followed to load the CLUT:

a) Program the CLUT address into the DMA2D_FGCMAR register (foreground

CLUT) or DMA2D_BGCMAR register (background CLUT)

b) Program the CLUT size in the CS[7:0] field of the DMA2D_FGPFCCR register

(foreground CLUT) or DMA2D_BGPFCCR register (background CLUT).

c) Set the START bit of the DMA2D_FGPFCCR register (foreground CLUT) or

DMA2D_BGPFCCR register (background CLUT) to start the transfer. During this

automatic loading process, the CLUT is not accessible by the CPU. If a conflict

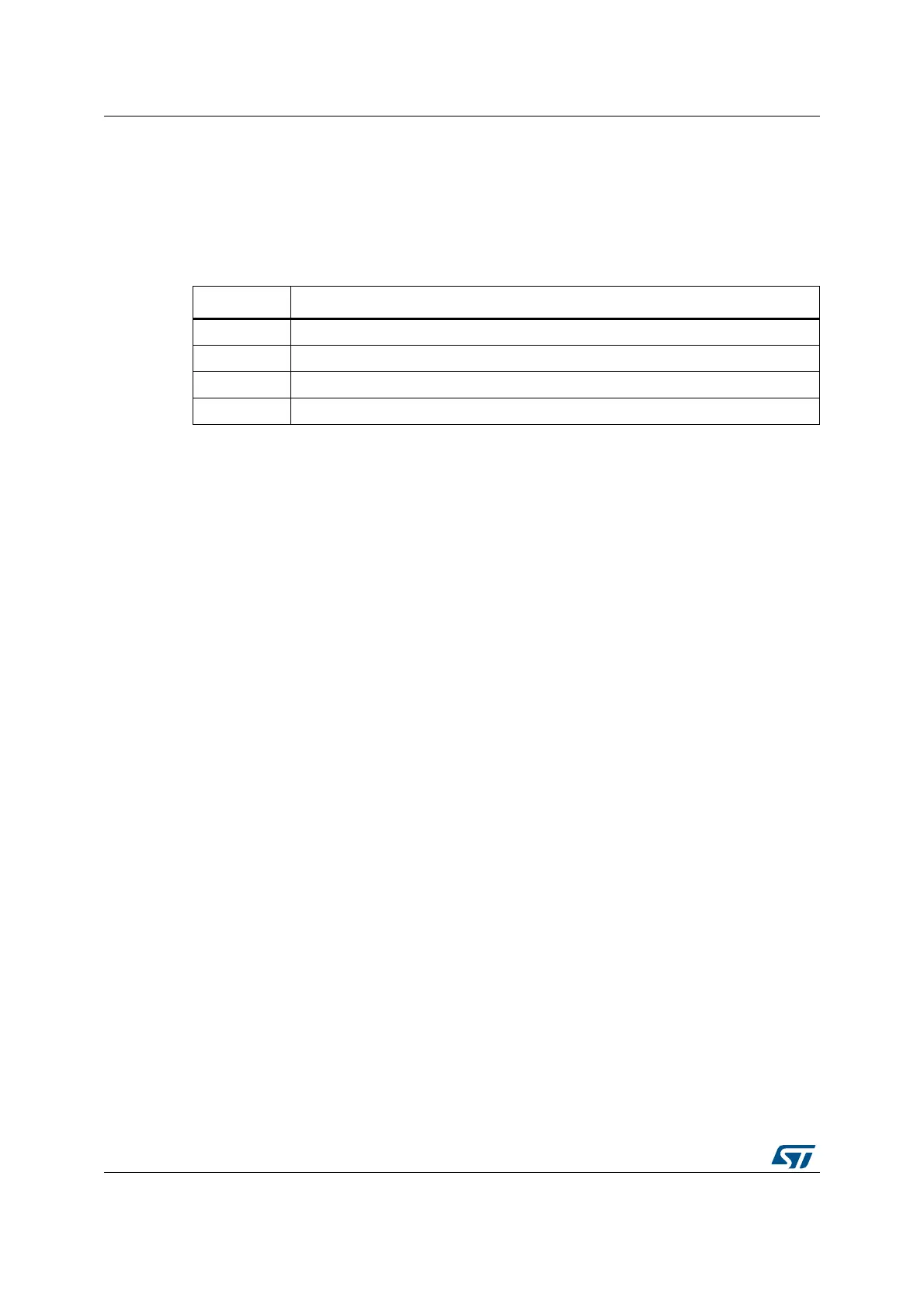

Table 50. Alpha mode configuration

AM[1:0] Alpha mode

00 No modification

01 Replaced by value in DMA2D_xxPFCCR

10 Replaced by original value multiplied by the value in DMA2D_xxPFCCR / 255

11 Reserved

Loading...

Loading...