Chrom-Art Accelerator™ controller (DMA2D) RM0351

370/1830 DocID024597 Rev 5

12.5 DMA2D registers

12.5.1 DMA2D control register (DMA2D_CR)

Address offset: 0x0000

Reset value: 0x0000 0000

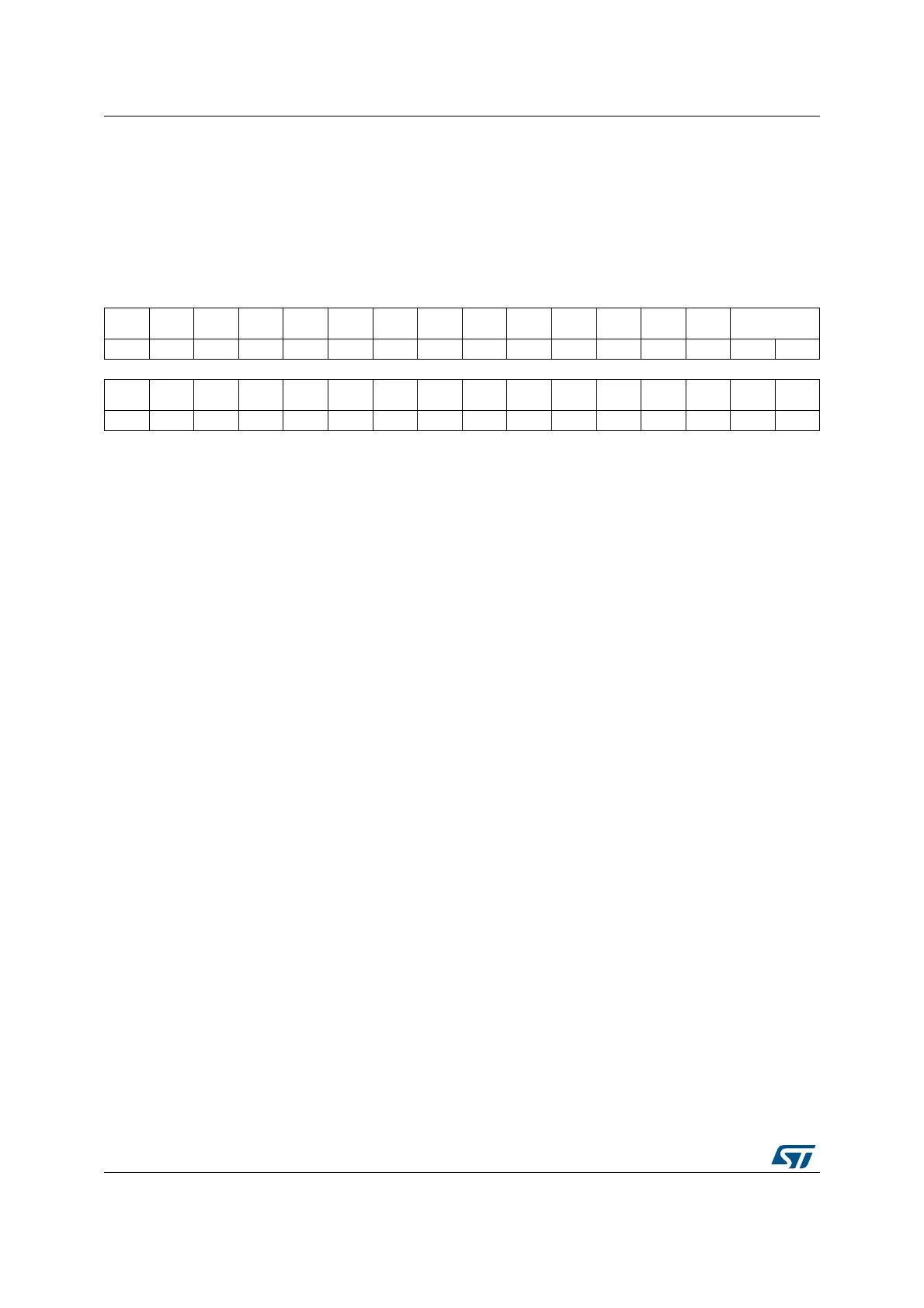

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. MODE[1:0]

rw rw

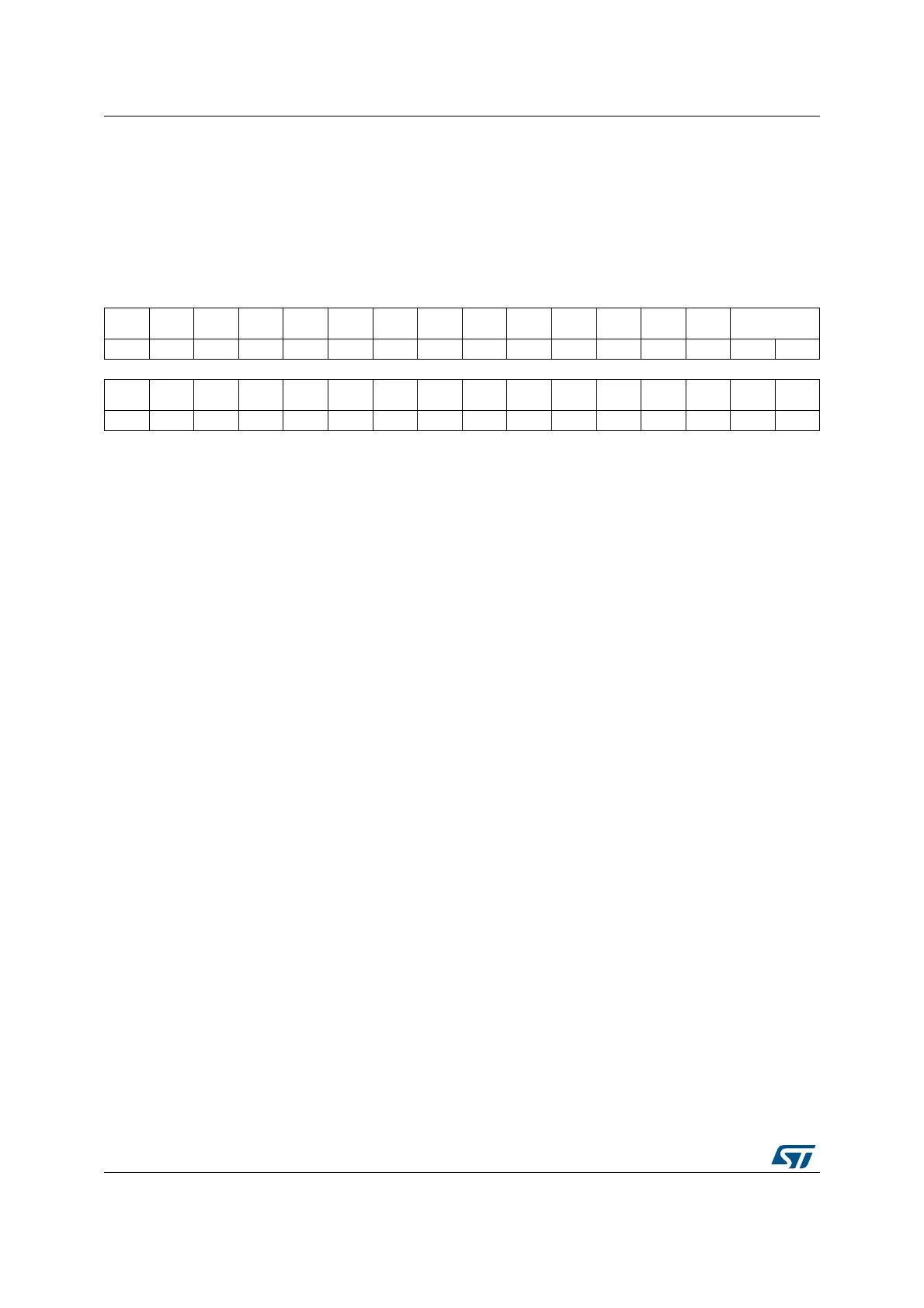

1514131211109876543210

Res. Res. CEIE CTCIE CAEIE TWIE TCIE TEIE Res. Res. Res. Res. Res. ABORT SUSP START

rw rw rw rw rw rw rs rw rs

Bits 31:18 Reserved, must be kept at reset value

Bits 17:16 MODE[1:0]: DMA2D mode

These bits are set and cleared by software. They cannot be modified while a transfer is

ongoing.

00: Memory-to-memory (FG fetch only)

01: Memory-to-memory with PFC (FG fetch only with FG PFC active)

10: Memory-to-memory with blending (FG and BG fetch with PFC and blending)

11: Register-to-memory (no FG nor BG, only output stage active)

Bits 15:14 Reserved, must be kept at reset value

Bit 13 CEIE: Configuration Error Interrupt Enable

This bit is set and cleared by software.

0: CE interrupt disable

1: CE interrupt enable

Bit 12 CTCIE: CLUT transfer complete interrupt enable

This bit is set and cleared by software.

0: CTC interrupt disable

1: CTC interrupt enable

Bit 11 CAEIE: CLUT access error interrupt enable

This bit is set and cleared by software.

0: CAE interrupt disable

1: CAE interrupt enable

Bit 10 TWIE: Transfer watermark interrupt enable

This bit is set and cleared by software.

0: TW interrupt disable

1: TW interrupt enable

Bit 9 TCIE: Transfer complete interrupt enable

This bit is set and cleared by software.

0: TC interrupt disable

1: TC interrupt enable

Loading...

Loading...