Nested vectored interrupt controller (NVIC) RM0351

396/1830 DocID024597 Rev 5

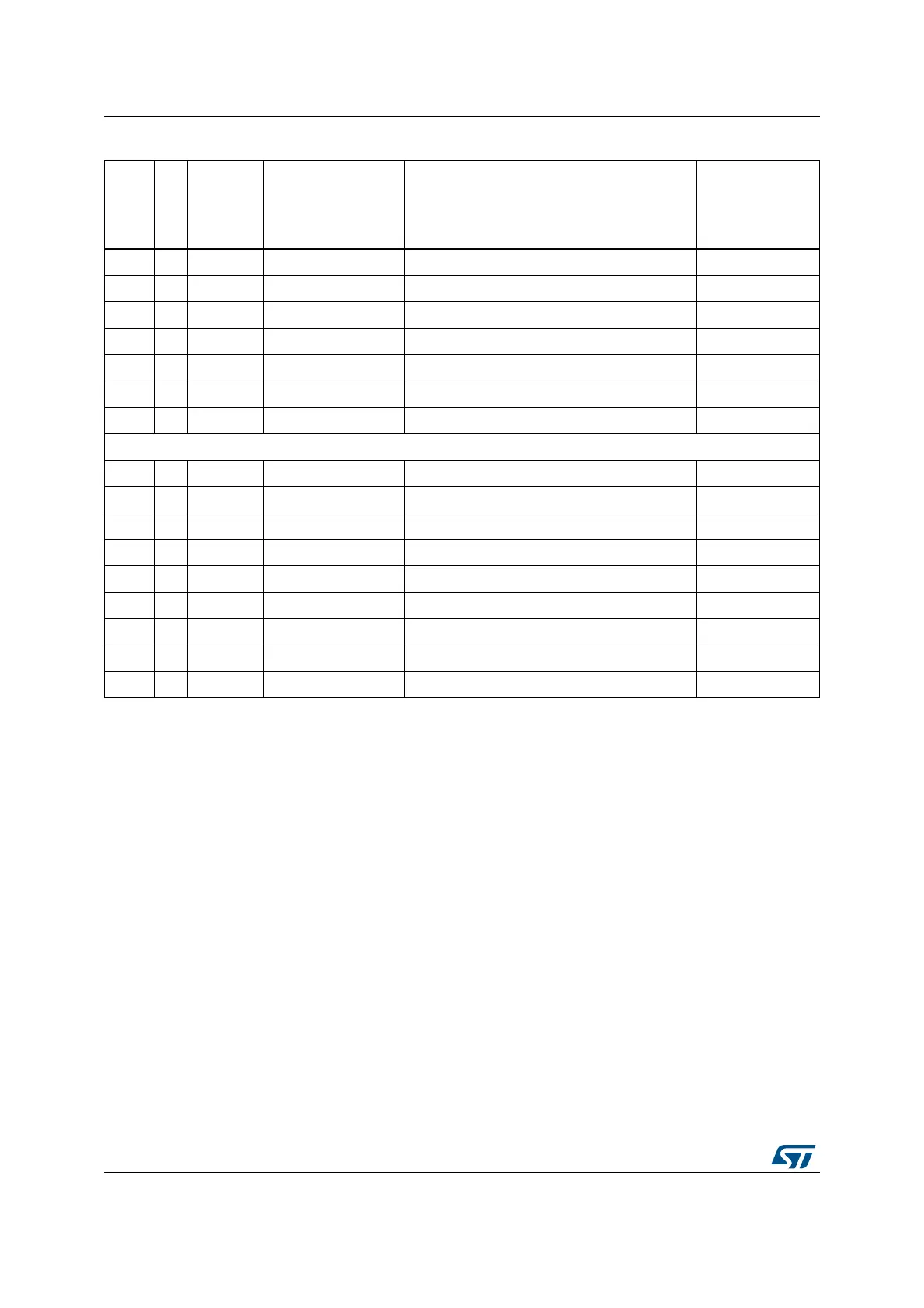

75 82 settable SAI2 SAI2 global interrupt 0x0000 016C

76 83 settable SWPMI1 SWPMI1 global interrupt 0x0000 0170

77 84 settable TSC TSC global interrupt 0x0000 0174

78 85 settable LCD LCD global interrupt 0x0000 0178

79 86 settable AES AES global interrupt 0x0000 017C

80 87 settable RNG RNG global interrupt 0x0000 0180

81 88 settable FPU Floating point interrupt 0x0000 0184

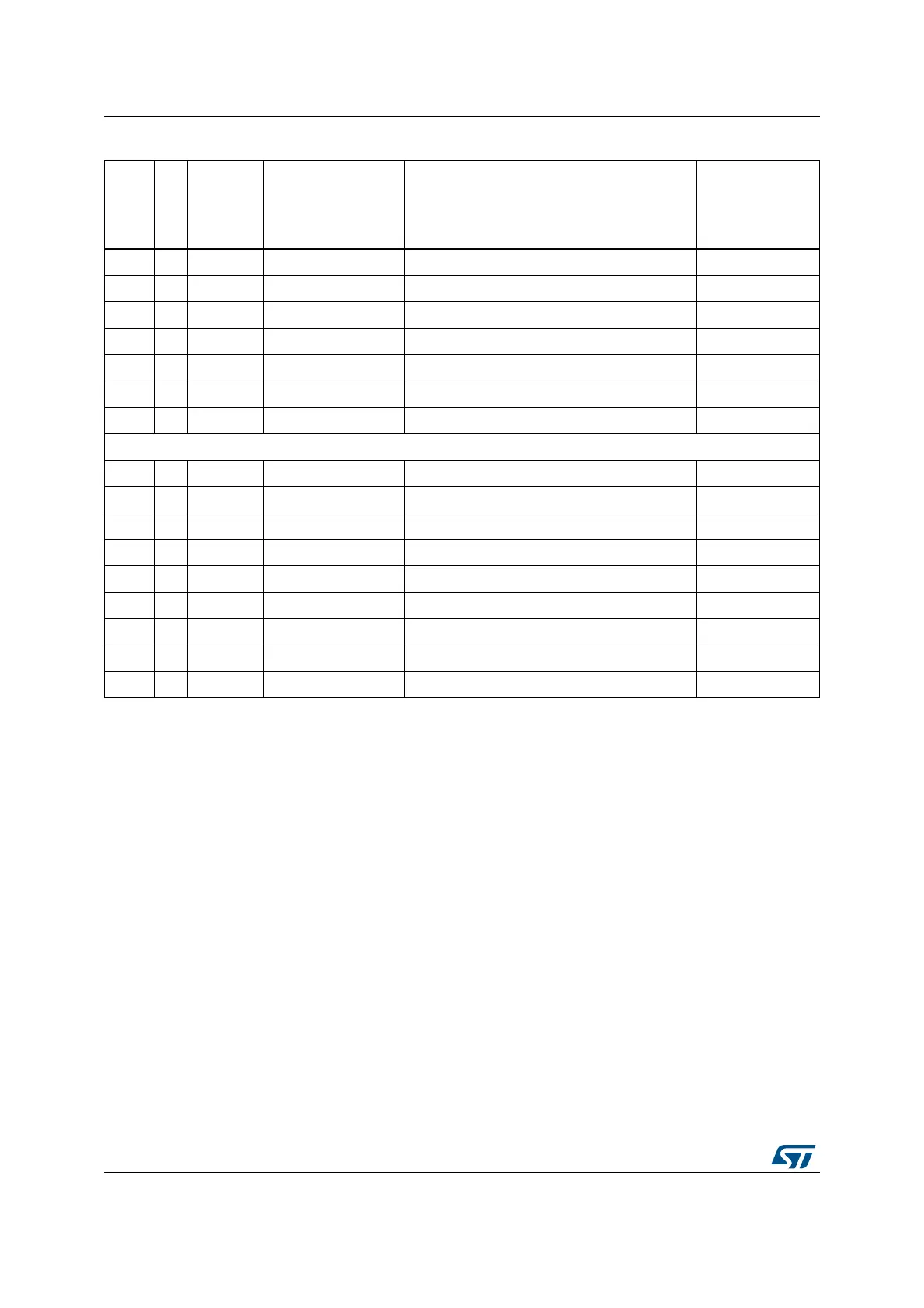

STM32L496xx/4A6xx devices

82 89 settable HASH and CRS

(1)

HASH and CRS interrupt 0x0000 0188

83 90 settable I2C4_EV I2C4 event interrupt 0x0000 018C

84 91 settable I2C4_ER I2C4 error interrupt 0x0000 0190

85 92 settable DCMI DCMI global interrupt 0x0000 0194

86 93 settable CAN2_TX CAN2 TX interrupt 0x0000 0198

87 94 settable CAN2_RX0 CAN2 RX0 interrupt 0x0000 019C

88 95 settable CAN2_RX1 CAN2 RX1 interrupt 0x0000 01A0

89 96 settable CAN2_SCE CAN SCE interrupt 0x0000 01A4

90 97 settable DMA2D DMA2D global interrupt 0x0000 01A8

1. HASH is only for STM32L496xx/4A6xx devices

Table 57. STM32L4x5/STM32L4x6 vector table (continued)

Position

Priority

Type of

priority

Acronym Description Address

Loading...

Loading...