Controller area network (bxCAN) RM0008

520/690

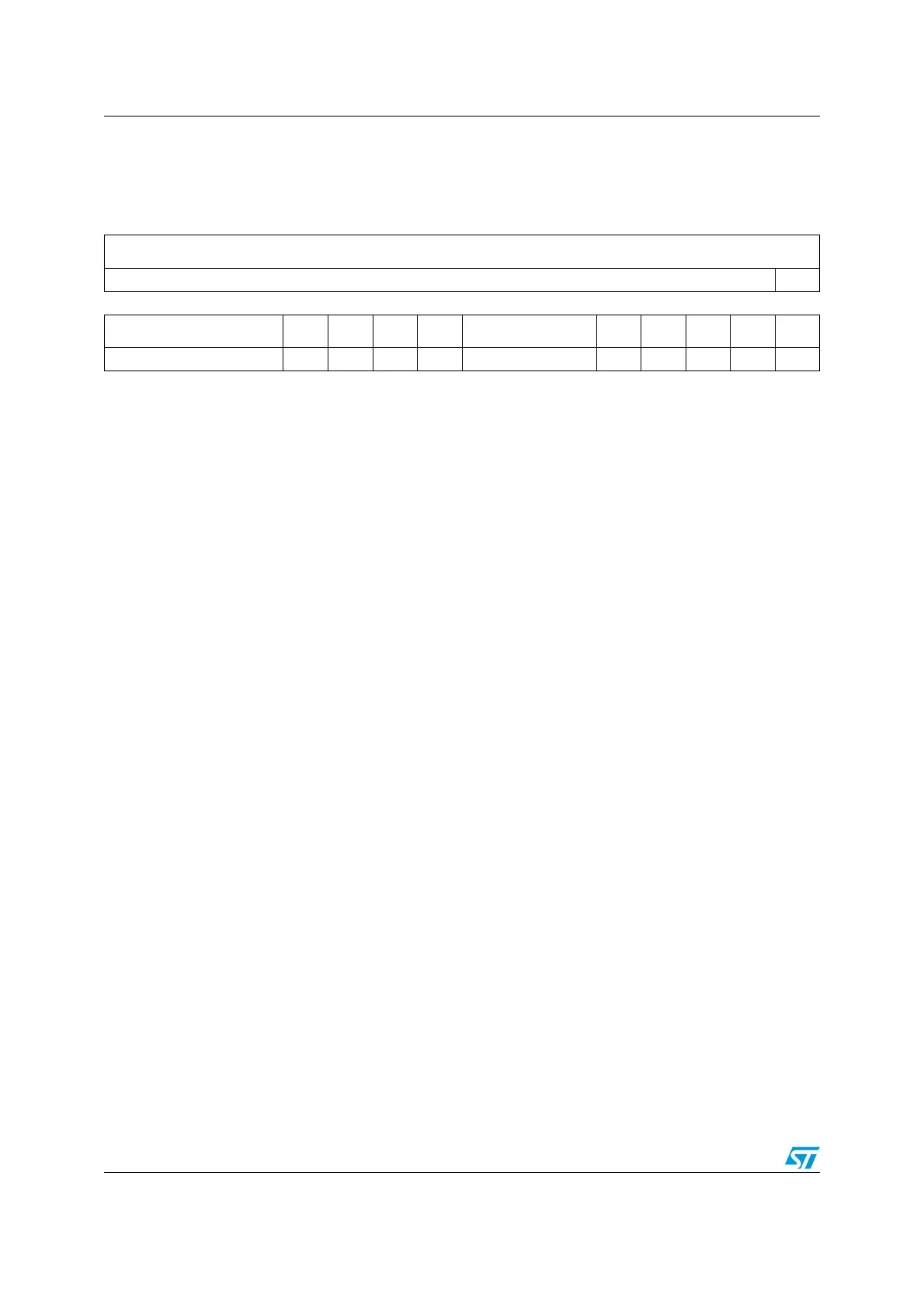

CAN master status register (CAN_MSR)

Address offset: 0x04

Reset value: 0x0000 0C02

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

Res. rw

1514131211109876543210

Reserved RX SAMP RXM TXM Reserved SLAKI WKUI ERRI SLAK INAK

Res. rrrr Res. rc_w1rc_w1rc_w1rr

Bits 31:12 Reserved, forced by hardware to 0.

Bit 11 RX: CAN Rx Signal

Monitors the actual value of the CAN_RX Pin.

Bit 10 SAMP: Last Sample Point

The value of RX on the last sample point (current received bit value).

Bit 9 RXM: Receive Mode

The CAN hardware is currently receiver.

Bit 8 TXM: Transmit Mode

The CAN hardware is currently transmitter.

Bits 7:5 Reserved, forced by hardware to 0.

Bit 4 SLAKI: Sleep Acknowledge Interrupt

When SLKIE=1, this bit is set by hardware to signal that the bxCAN has entered Sleep Mode. When

set, this bit generates a status change interrupt if the SLKIE bit in the CAN_IER register is set.

This bit is cleared by software or by hardware, when SLAK is cleared.

Note: When SLKIE=0, no polling on SLAKI is possible. In this case the SLAK bit can be polled.

Bit 3 WKUI: Wakeup Interrupt

This bit is set by hardware to signal that a SOF bit has been detected while the CAN hardware was

in Sleep mode. Setting this bit generates a status change interrupt if the WKUIE bit in the CAN_IER

register is set.

This bit is cleared by software.

Loading...

Loading...