DocID024597 Rev 5 1449/1830

RM0351 Serial audio interface (SAI)

1490

43.3 SAI functional description

43.3.1 SAI block diagram

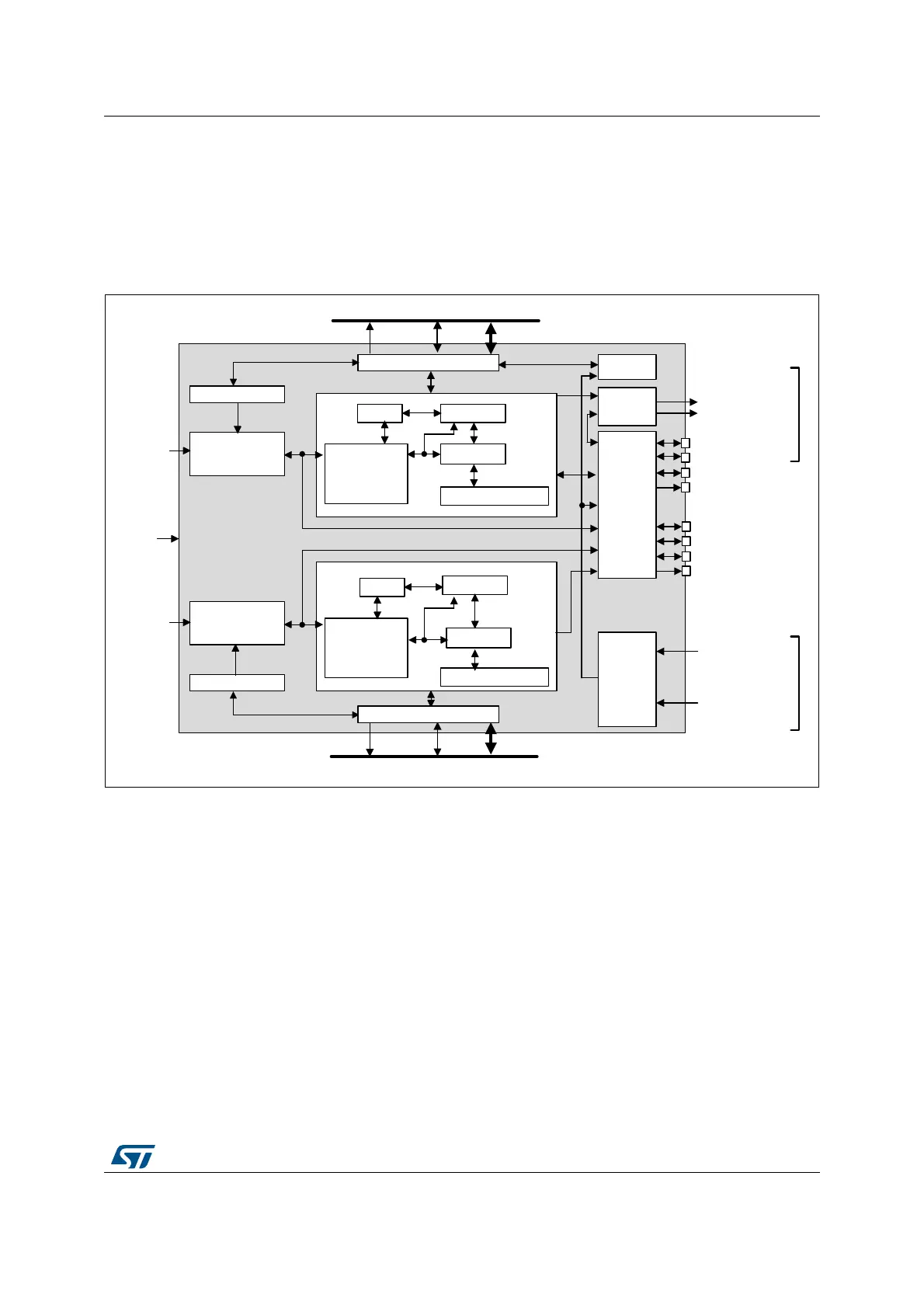

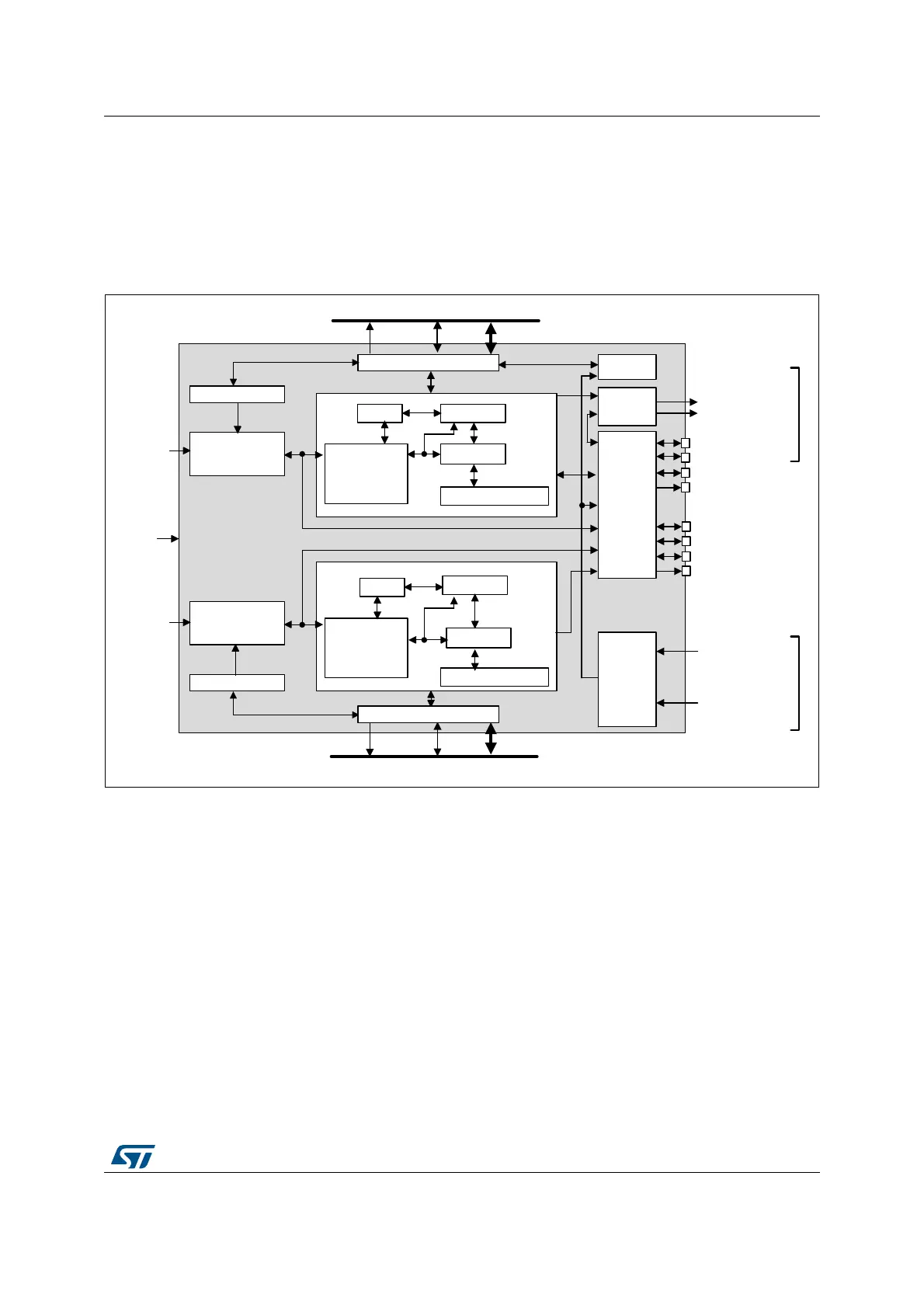

Figure 459 shows the SAI block diagram while Table 251 and Table 252 list SAI internal and

external signals.

Figure 459. Functional block diagram

The SAI is mainly composed of two audio sub-blocks with their own clock generator. Each

audio block integrates a 32-bit shift register controlled by their own functional state machine.

Data are stored or read from the dedicated FIFO. FIFO may be accessed by the CPU, or by

DMA in order to leave the CPU free during the communication. Each audio block is

independent. They can be synchronous with each other.

An I/O line controller manages a set of 4 dedicated pins (SD, SCK, FS, MCLK) for a given

audio block in the SAI. Some of these pins can be shared if the two sub-blocks are declared

as synchronous to leave some free to be used as general purpose I/Os. The MCLK pin can

be output, or not, depending on the application, the decoder requirement and whether the

audio block is configured as the master.

If one SAI is configured to operate synchronously with another one, even more I/Os can be

freed (except for pins SD_x).

The functional state machine can be configured to address a wide range of audio protocols.

Some registers are present to set-up the desired protocols (audio frame waveform

generator).

06Y9

),)2 ),)2FWUO

&RQILJXUDWLRQ

DQGVWDWXV

UHJLVWHUV

)60

ELWVKLIWUHJLVWHU

$XGLREORFN$

),)2

),)2FWUO

&RQILJXUDWLRQ

DQGVWDWXV

UHJLVWHUV

)60

ELWVKLIWUHJLVWHU

$XGLREORFN%

&ORFNJHQHUDWRU

$XGLREORFN$

6$,B$&5

6$,B%&5

&ORFNJHQHUDWRU

$XGLREORFN%

$3%,QWHUIDFH

6$,B*&5

6\QFKUR

FWUORXW

,2/LQH0DQDJHPHQW

6\QFKUR

LQ

6$,

VDLBDB

NHUBFN

VDLBEB

NHUBFN

)6B$

6'B$

6&.B$

0&/.B$

)6B%

6'B%

6&.B%

0&/.B%

ELW$3%EXV

ELW$3%EXV

)URPRWKHU6$,%ORFNV

VDLBDBJEOBLW

VDLBEBJEOBLW

VDLBEBGPD

VDLBDBGPD

7RRWKHU6$,%ORFNV

VDLBV\QFBRXWBVFN

VDLBV\QFBRXWBIV

VDLBV\QFBLQBVFN

VDLBV\QFBLQBIV

VDLBSFON

$3%,QWHUIDFH

Loading...

Loading...