DocID024597 Rev 5 1561/1830

RM0351 SD/SDIO/MMC card host interface (SDMMC)

1575

Note: 1 While the SD/SDIO card or MultiMediaCard is in identification mode, the SDMMC_CK

frequency must be less than 400 kHz.

2 The clock frequency can be changed to the maximum card bus frequency when relative

card addresses are assigned to all cards.

3 After a data write, data cannot be written to this register for three SDMMCCLK clock periods

plus two PCLK2 clock periods. SDMMC_CK can also be stopped during the read wait

interval for SD I/O cards: in this case the SDMMC_CLKCR register does not control

SDMMC_CK.

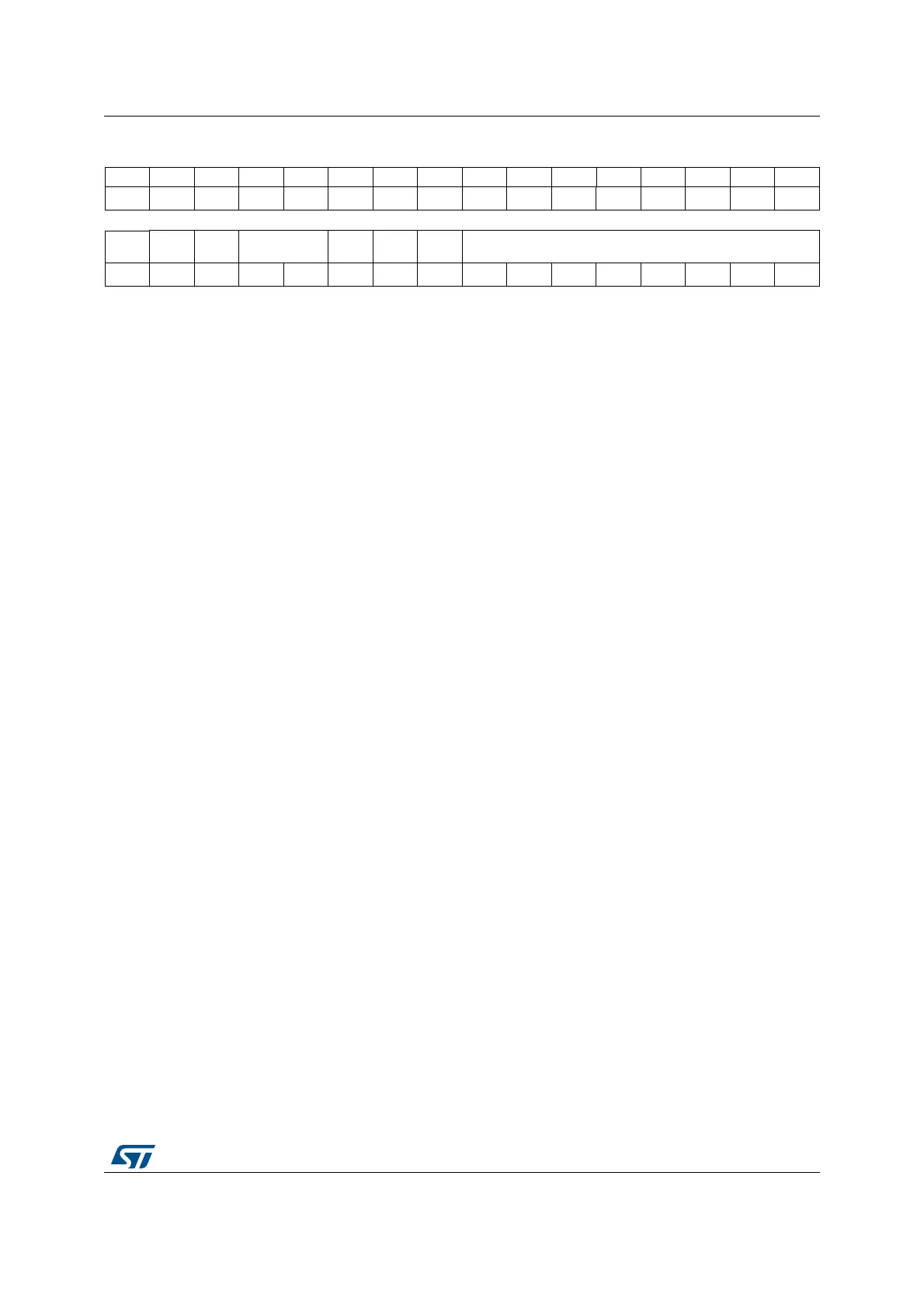

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res.

HWFC

_EN

NEGE

DGE

WID

BUS

BYPAS

S

PWRS

AV

CLKEN CLKDIV

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:15 Reserved, must be kept at reset value.

Bit 14 HWFC_EN: HW Flow Control enable

0b: HW Flow Control is disabled

1b: HW Flow Control is enabled

When HW Flow Control is enabled, the meaning of the TXFIFOE and RXFIFOF interrupt

signals, see SDMMC Status register definition in Section 45.8.11.

Bit 13 NEGEDGE: SDMMC_CK dephasing selection bit

0b: Command and Data changed on the SDMMCCLK falling edge succeeding the rising

edge of SDMMC_CK. (SDMMC_CK rising edge occurs on SDMMCCLK rising edge).

1b: Command and Data changed on the SDMMC_CK falling edge.

When BYPASS is active, the data and the command change on SDMMCCLK falling edge

whatever NEGEDGE value.

Bits 12:11 WIDBUS: Wide bus mode enable bit

00: Default bus mode: SDMMC_D0 used

01: 4-wide bus mode: SDMMC_D[3:0] used

10: 8-wide bus mode: SDMMC_D[7:0] used

Bit 10 BYPASS: Clock divider bypass enable bit

0: Disable bypass: SDMMCCLK is divided according to the CLKDIV value before driving the

SDMMC_CK output signal.

1: Enable bypass: SDMMCCLK directly drives the SDMMC_CK output signal.

Bit 9 PWRSAV: Power saving configuration bit

For power saving, the SDMMC_CK clock output can be disabled when the bus is idle by

setting PWRSAV:

0: SDMMC_CK clock is always enabled

1: SDMMC_CK is only enabled when the bus is active

Bit 8 CLKEN: Clock enable bit

0: SDMMC_CK is disabled

1: SDMMC_CK is enabled

Bits 7:0 CLKDIV: Clock divide factor

This field defines the divide factor between the input clock (SDMMCCLK) and the output

clock (SDMMC_CK): SDMMC_CK frequency = SDMMCCLK / [CLKDIV + 2].

Loading...

Loading...