RM0008 Flexible static memory controller (FSMC)

397/690

SRAM/NOR-Flash write timing registers 1..4 (FSMC_BWTR1..4)

Address offset: 0xA000 0000 + 0x104 + 8 * (x – 1), x = 1...4

Reset value: 0x0FFF FFFF

This register contains the control information of each memory bank, used for SRAMs, ROMs

and NOR Flash memories. When the EXTMOD bit is set in the FSMC_BCRx register, then

this register is active for write access.

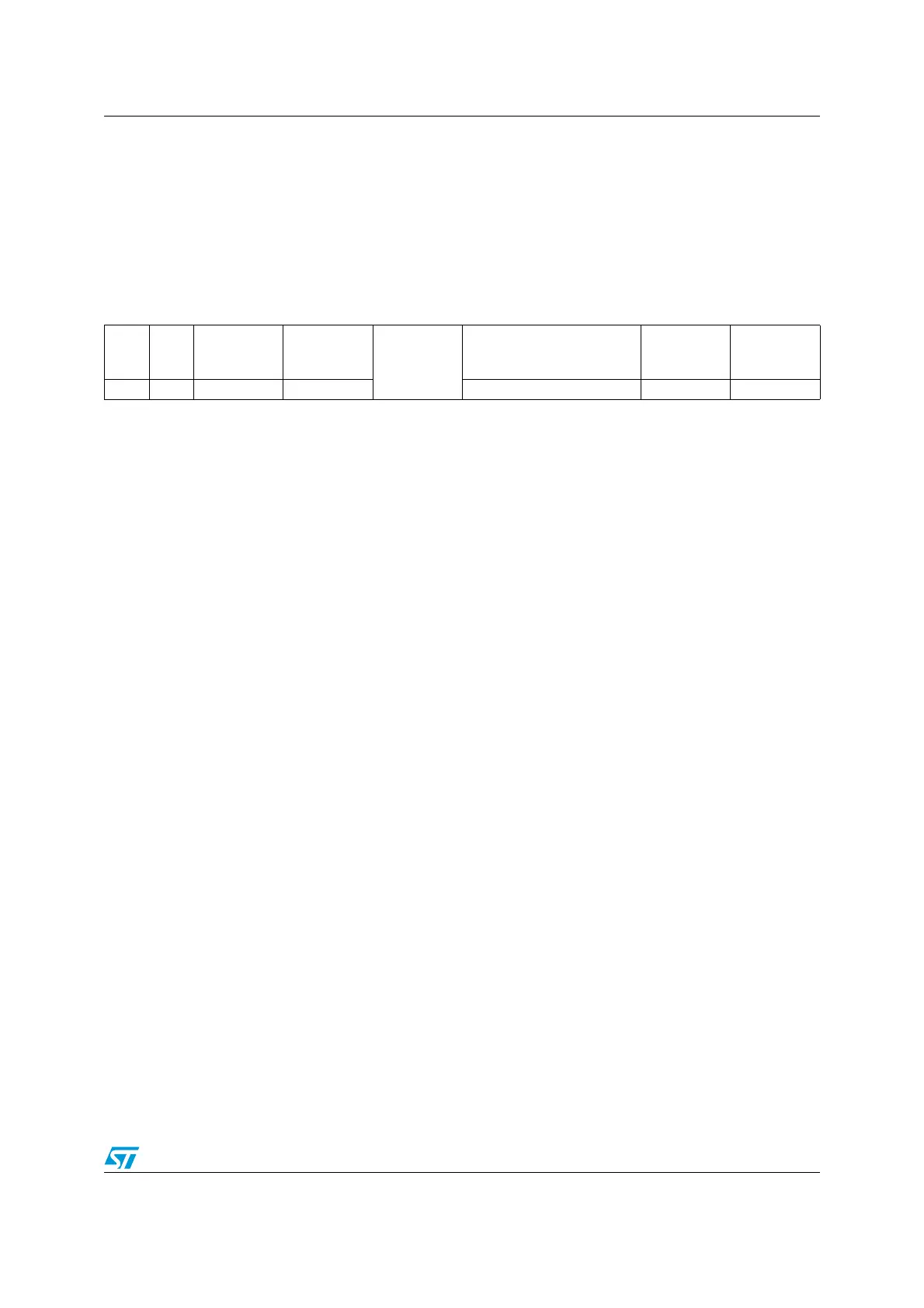

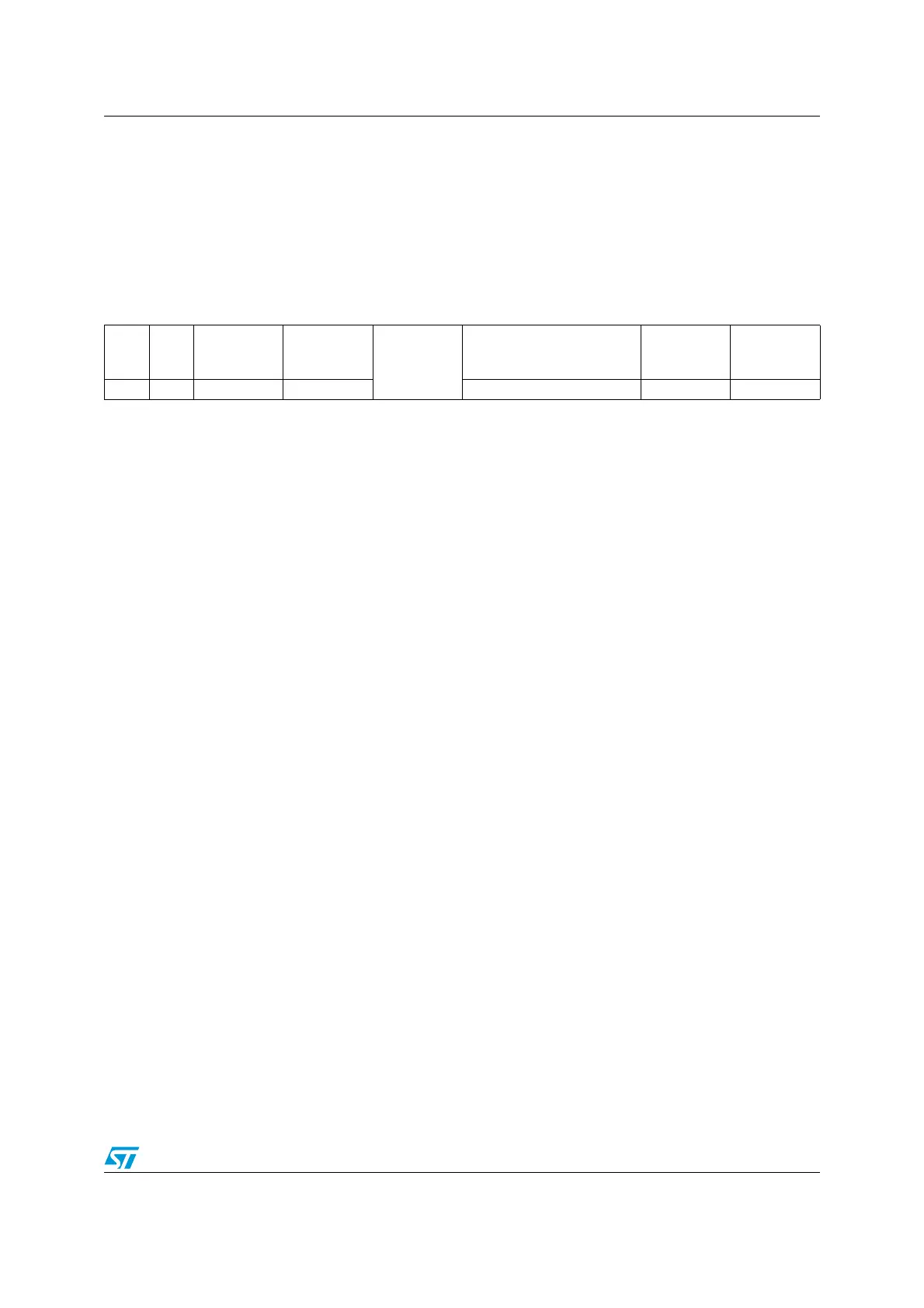

313029282726252423222120191817161514131211109876543210

Reserved

ACCMOD

DATLAT

CLKDIV

Reserved

DATAST

ADDHLD

ADDSET

r r/w r/w r/w r/w r/w r/w

Bits 29:28 ACCMOD: Access mode.

Specifies the asynchronous access modes as shown in the next timing diagrams.These bits are

taken into account only when the EXTMOD bit in the FSMC_BCRx register is 1.

00: access mode A

01: access mode B

10: access mode C

11: access mode D

Bits 27:24 DATLAT: Data latency (for synchronous burst NOR Flash).

For NOR Flash with Synchronous burst mode enabled, defines the number of memory clock cycles

(+2) to issue to the memory before getting the first data:

0000: (0x0) Data latency of 2 CLK clock cycles for first burst access

...

1111: (0xF) Data latency of 17 CLK clock cycles for first burst access (default value after reset)

Note: This timing parameter is not expressed in HCLK periods, but in Flash clock (CLK) periods

Note: In asynchronous NOR Flash, SRAM or ROM accesses, this value is don’t care.

Note: In case of CRAM, this field must be set to 0

Bits 23:20 CLKDIV: Clock divide ratio (for CLK signal).

Defines the period of CLK clock output signal, expressed in number of HCLK cycles:

0000: Reserved

0001 CLK period = 2 × HCLK periods

0010 CLK period = 3 × HCLK periods

1111: CLK period = 16 × HCLK periods (default value after reset)

In asynchronous NOR Flash, SRAM or ROM accesses, this value is don’t care.

Bits 19:16 Reserved

Loading...

Loading...