RM0440 Rev 4 1001/2126

RM0440 High-resolution timer (HRTIM)

1083

27.5.32 HRTIM timer x external event filtering register 2 (HRTIM_EEFxR2)

(x = A to F)

Address offset: Block A: 0x0D0

Address offset: Block B: 0x150

Address offset: Block C: 0x1D0

Address offset: Block D: 0x250

Address offset: Block E: 0x2D0

Address offset: Block F: 0x350

Reset value: 0x0000 0000

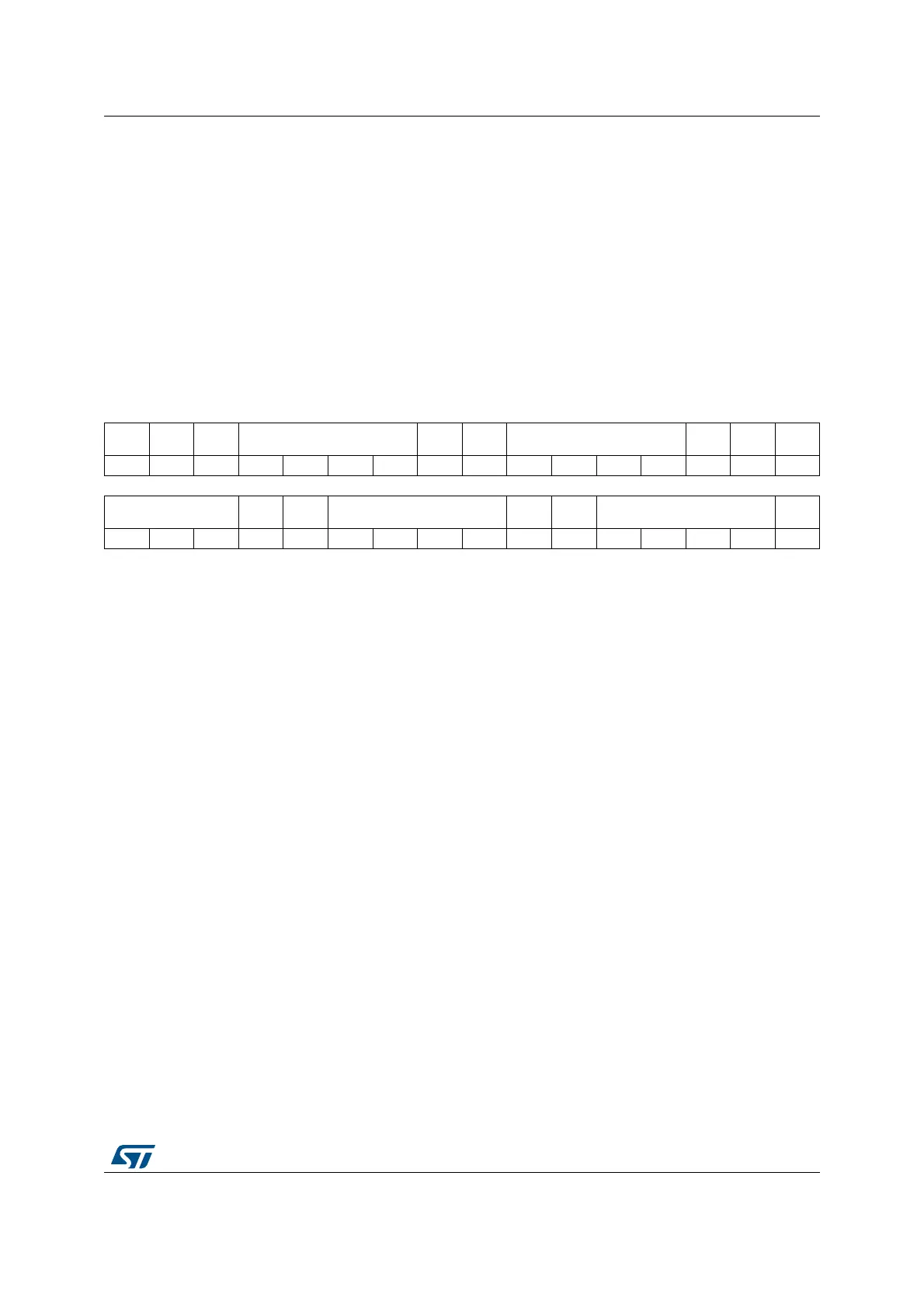

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. EE10FLTR[3:0]

EE10LT

CH

Res. EE9FLTR[3:0]

EE9LT

CH

Res.

EE8FL

TR[3]

rw rw rw rw rw rw rw rw rw rw rw

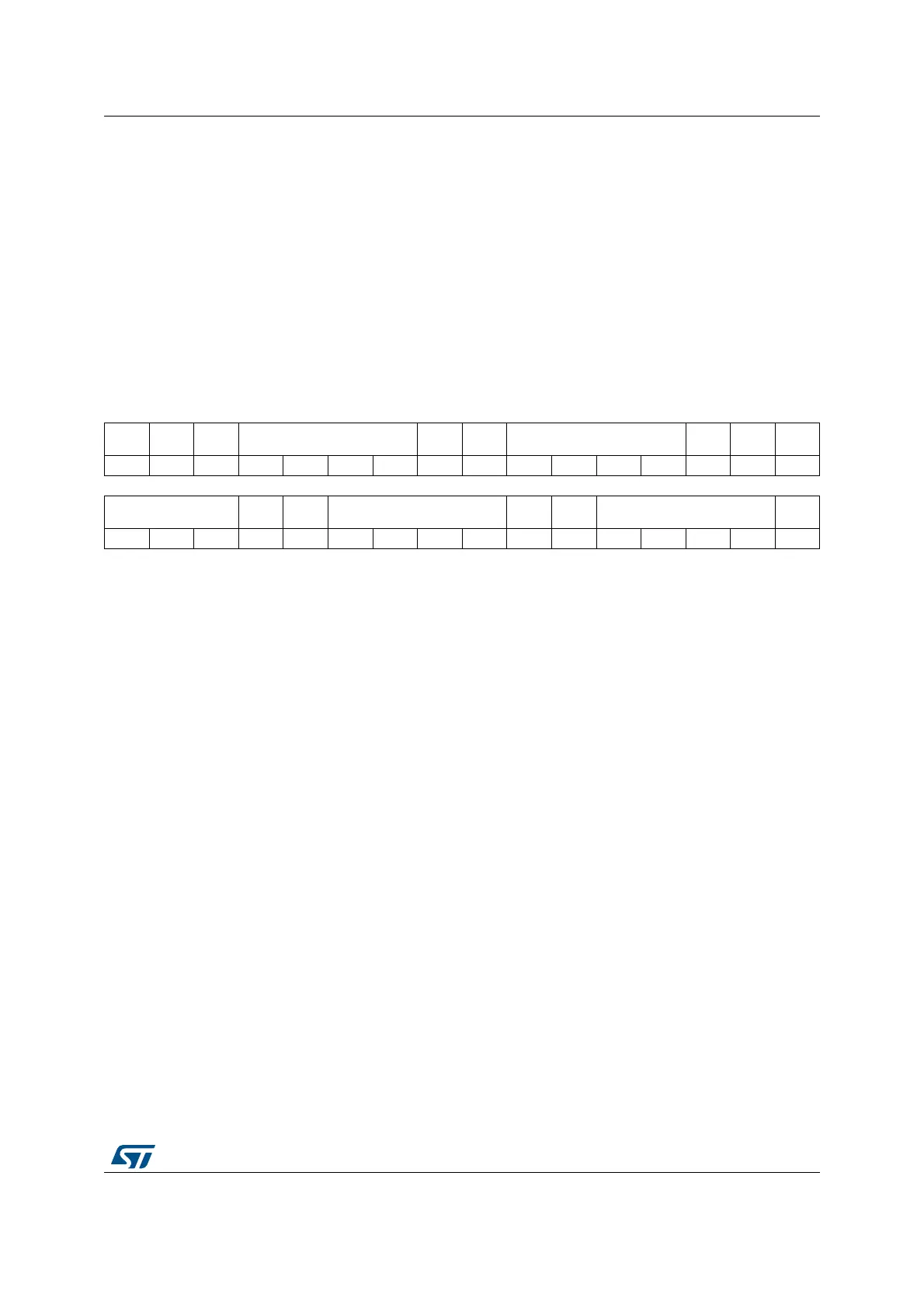

1514131211109876543210

EE8FLTR[2:0]

EE8LT

CH

Res. EE7FLTR[3:0]

EE7LT

CH

Res. EE6FLTR[3:0]

EE6LT

CH

rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:29 Reserved, must be kept at reset value.

Bits 28:25 EE10FLTR[3:0]: External event 10 filter

Refer to EE1FLTR[3:0] description.

Bit 24 EE10LTCH: External event 10 latch

Refer to EE1LTCH description.

Bit 23 Reserved, must be kept at reset value.

Bits 22:19 EE9FLTR[3:0]: External event 9 filter

Refer to EE1FLTR[3:0] description.

Bit 18 EE9LTCH: External event 9 latch

Refer to EE1LTCH description.

Bit 17 Reserved, must be kept at reset value.

Bits 16:13 EE8FLTR[3:0]: External event 8 filter

Refer to EE1FLTR[3:0] description.

Bit 12 EE8LTCH: External event 8 latch

Refer to EE1LTCH description.

Bit 11 Reserved, must be kept at reset value.

Bits 10:7 EE7FLTR[3:0]: External event 7 filter

Refer to EE1FLTR[3:0] description.

Bit 6 EE7LTCH: External event 7 latch

Refer to EE1LTCH description.

Loading...

Loading...