Analog-to-digital converters (ADC) RM0440

626/2126 RM0440 Rev 4

21.4.18 Conversion on external trigger and trigger polarity

(EXTSEL, EXTEN,JEXTSEL, JEXTEN)

A conversion or a sequence of conversions can be triggered either by software or by an

external event (e.g. timer capture, input pins). If the EXTEN[1:0] control bits (for a regular

conversion) or JEXTEN[1:0] bits (for an injected conversion) are different from 0b00, then

external events are able to trigger a conversion with the selected polarity.

When the Injected Queue is enabled (bit JQDIS=0), injected software triggers are not

possible.

The regular trigger selection is effective once software has set bit ADSTART=1 and the

injected trigger selection is effective once software has set bit JADSTART=1.

Any hardware triggers which occur while a conversion is ongoing are ignored.

• If bit ADSTART=0, any regular hardware triggers which occur are ignored.

• If bit JADSTART=0, any injected hardware triggers which occur are ignored.

Table 161 provides the correspondence between the EXTEN[1:0] and JEXTEN[1:0] values

and the trigger polarity.

Note: The polarity of the regular trigger cannot be changed on-the-fly.

Note: The polarity of the injected trigger can be anticipated and changed on-the-fly when the

queue is enabled (JQDIS=0). Refer to Section 21.4.21: Queue of context for injected

conversions.

The EXTSEL and JEXTSEL control bits select which out of 32 possible events can trigger

conversion for the regular and injected groups.

A regular group conversion can be interrupted by an injected trigger.

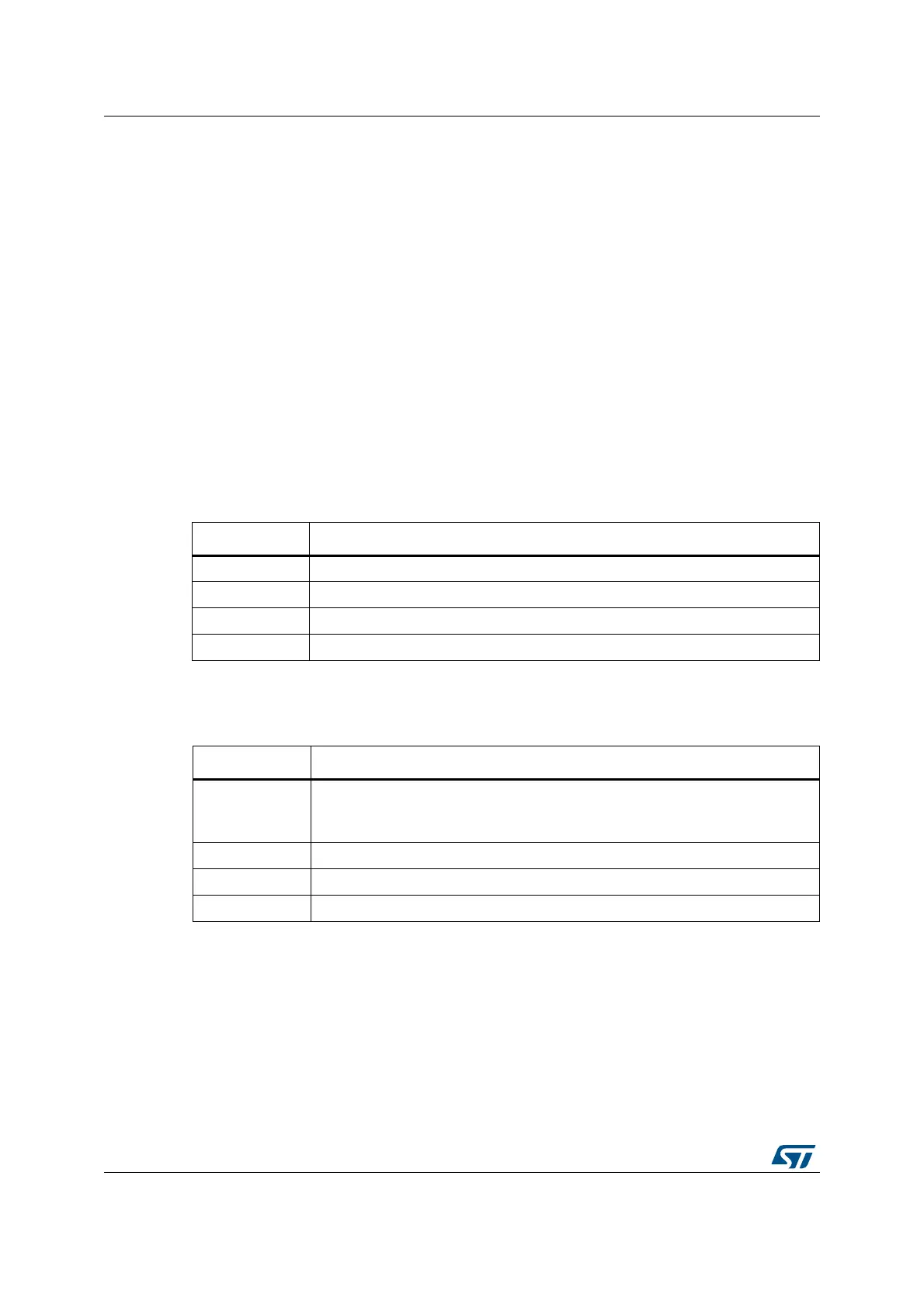

Table 161. Configuring the trigger polarity for regular external triggers

EXTEN[1:0] Source

00 Hardware Trigger detection disabled, software trigger detection enabled

01 Hardware Trigger with detection on the rising edge

10 Hardware Trigger with detection on the falling edge

11 Hardware Trigger with detection on both the rising and falling edges

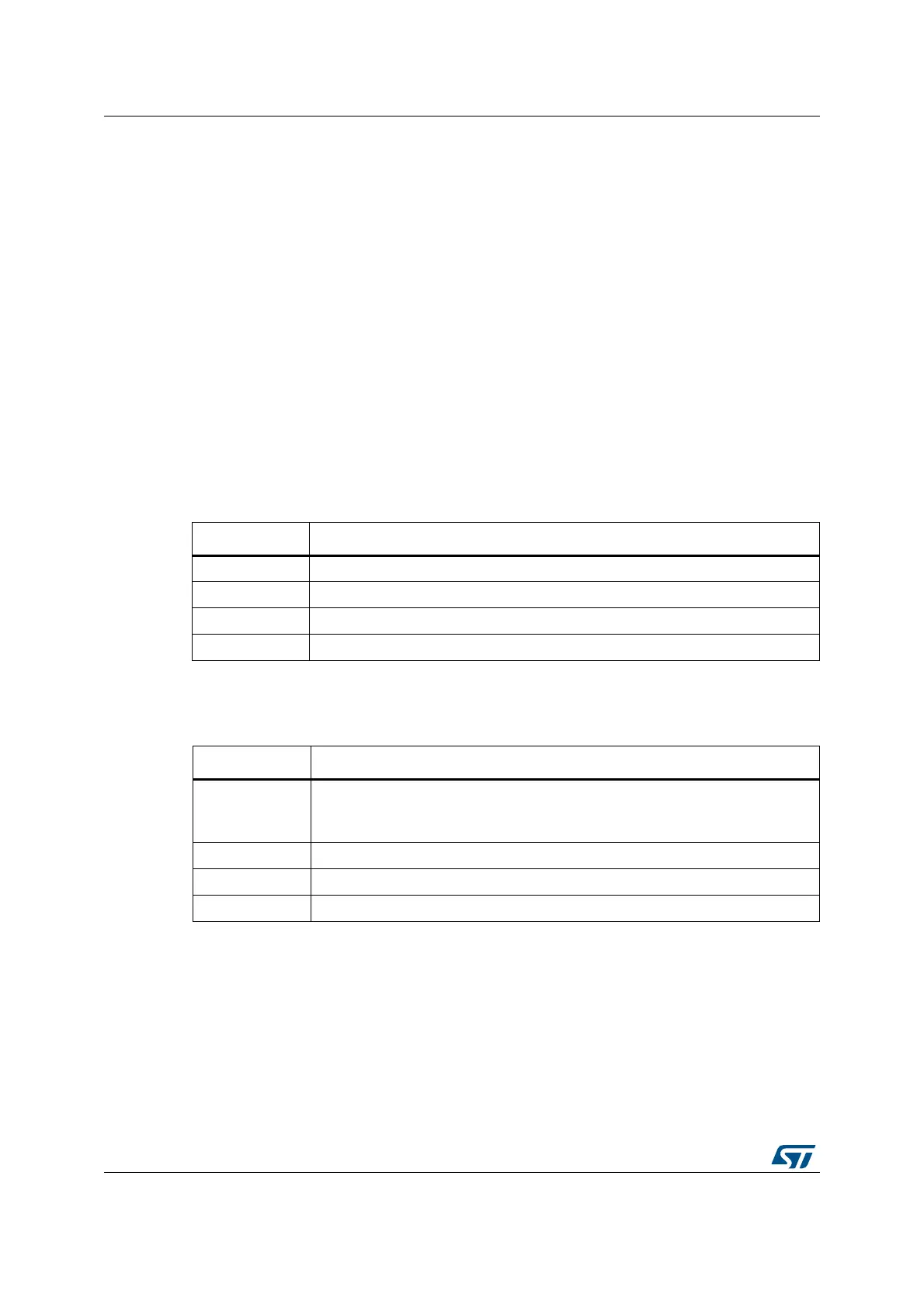

Table 162. Configuring the trigger polarity for injected external triggers

JEXTEN[1:0] Source

00

– If JQDIS=1 (Queue disabled): Hardware trigger detection disabled, software

trigger detection enabled

– If JQDIS=0 (Queue enabled), Hardware and software trigger detection disabled

01 Hardware Trigger with detection on the rising edge

10 Hardware Trigger with detection on the falling edge

11 Hardware Trigger with detection on both the rising and falling edges

Loading...

Loading...