RM0440

88/2126 RM0440 Rev 4

The write protection can be enabled in Section 10.2.9: SYSCFG CCM SRAM write

protection register (SYSCFG_SWPR) in the SYSCFG block. This is a register with write ‘1’

once mechanism, which means by writing ‘1’ on a bit it sets up the write protection for that

page of SRAM and it can be removed/cleared by a system reset only.

2.4.3 CCM SRAM read protection

The CCMSRAM is protected with the Read protection (RDP). Refer to Section 3.5.1: Read

protection (RDP) for more details.

2.4.4 CCM SRAM erase

The CCMSRAM can be erased with a system reset using the option bit CCMSRAM_RST in

the user option byte (refer to Section 3.4.1: Option bytes description).

The CCM SRAM erase can also be requested by software by setting the bit CCMSR in the

Section 10.2.7: SYSCFG CCM SRAM control and status register (SYSCFG_SCSR).

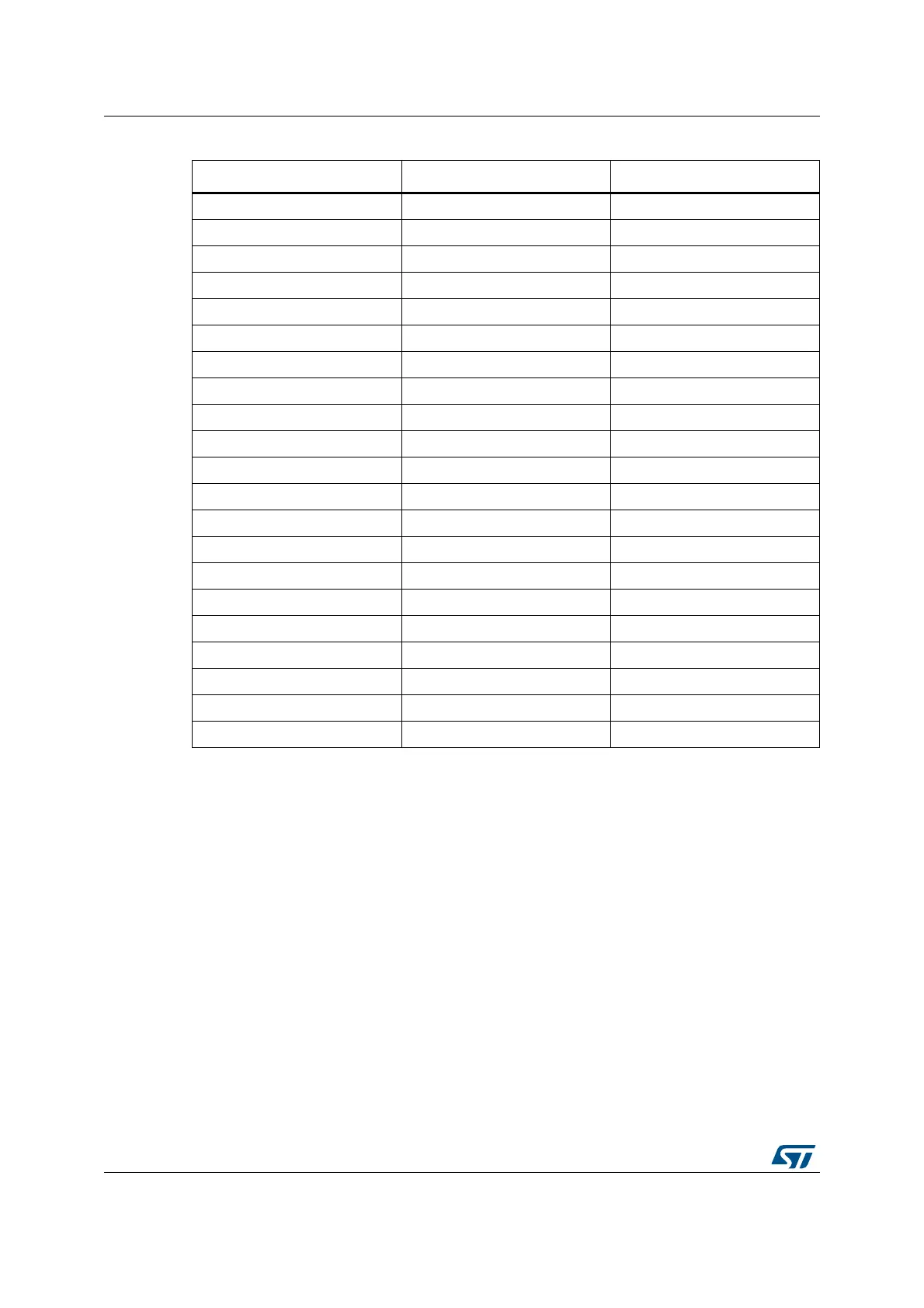

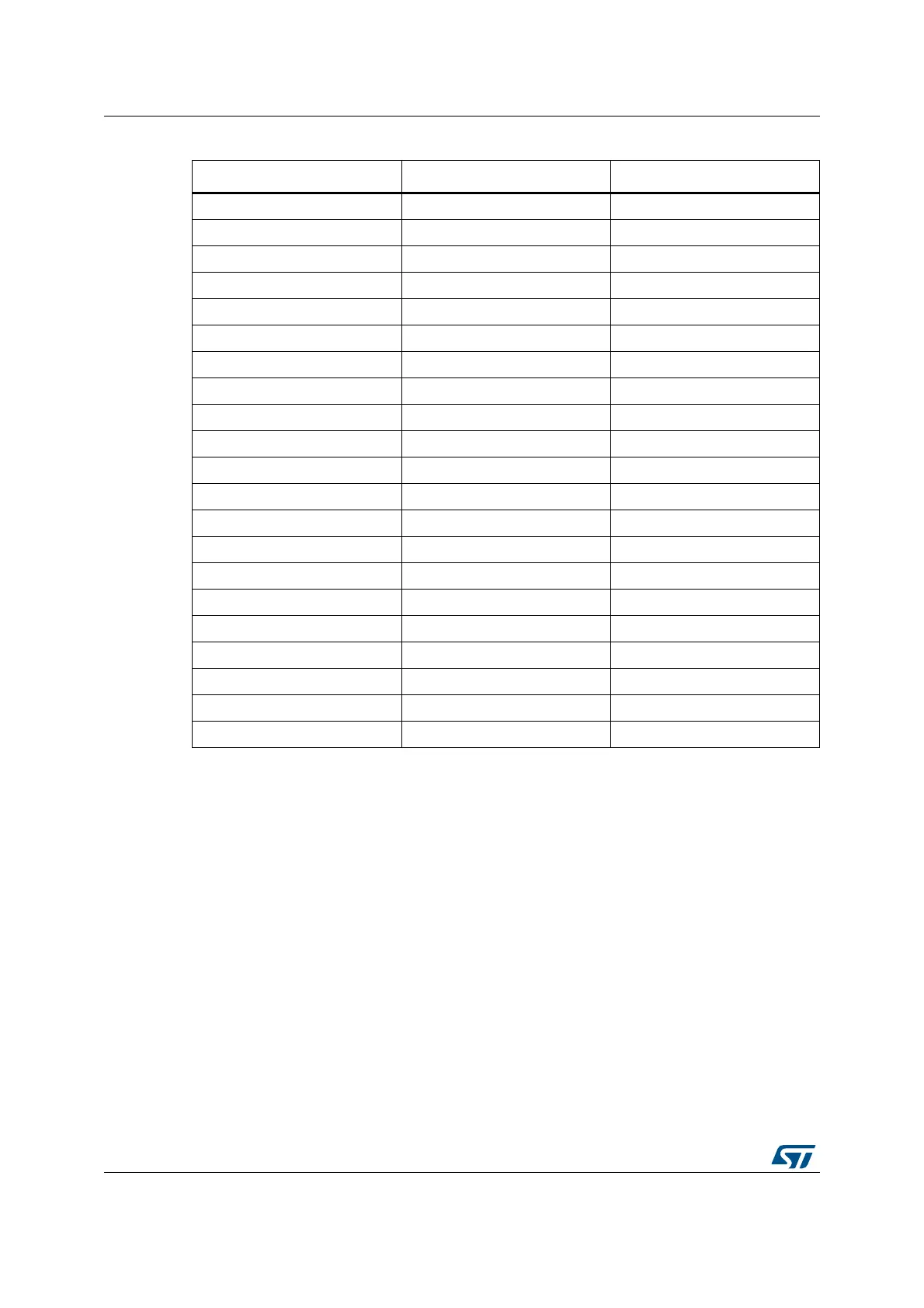

Page 11

(1)

0x1000 2C00 0x1000 2FFF

Page 12

(1)

0x1000 3000 0x1000 33FF

Page 13

(1)

0x1000 3400 0x1000 37FF

Page 14

(1)

0x1000 3800 0x1000 3BFF

Page 15

(1)

0x1000 3C00 0x1000 3FFF

Page 16

(2)

0x1000 4000 0x1000 43FF

Page 17

(2)

0x1000 4400 0x1000 47FF

Page 18

(2)

0x1000 4800 0x1000 4BFF

Page 19

(2)

0x1000 4C00 0x1000 4FFF

Page 20

(2)

0x1000 5000 0x1000 53FF

Page 21

(2)

0x1000 5400 0x1000 57FF

Page 22

(2)

0x1000 5800 0x1000 5BFF

Page 23

(2)

0x1000 5C00 0x1000 5FFF

Page 24

(2)

0x1000 6000 0x1000 63FF

Page 25

(2)

0x1000 6400 0x1000 67FF

Page 26

(2)

0x1000 6800 0x1000 6BFF

Page 27

(2)

0x1000 6C00 0x1000 6FFF

Page 28

(2)

0x1000 7000 0x1000 73FF

Page 29

(2)

0x1000 7400 0x1000 77FF

Page 30

(2)

0x1000 7800 0x1000 7BFF

Page 31

(2)

0x1000 7C00 0x1000 7FFF

1. Available on Category 3 and Category 4 devices only.

2. Available on Category 3 devices only.

Table 4. CCM SRAM organization (continued)

Page number Start address End address

Loading...

Loading...