Advanced-control timers (TIM1/TIM8/TIM20) RM0440

1138/2126 RM0440 Rev 4

Arming and re-arming break circuitry

The break circuitry (in input or bidirectional mode) is armed by default (peripheral reset

configuration).

The following procedure must be followed to re-arm the protection after a break (break2)

event:

• The BKDSRM (BK2DSRM) bit must be set to release the output control

• The software must wait until the system break condition disappears (if any) and clear

the SBIF status flag (or clear it systematically before re-arming)

• The software must poll the BKDSRM (BK2DSRM) bit until it is cleared by hardware

(when the application break condition disappears)

From this point, the break circuitry is armed and active, and the MOE bit can be set to re-

enable the PWM outputs.

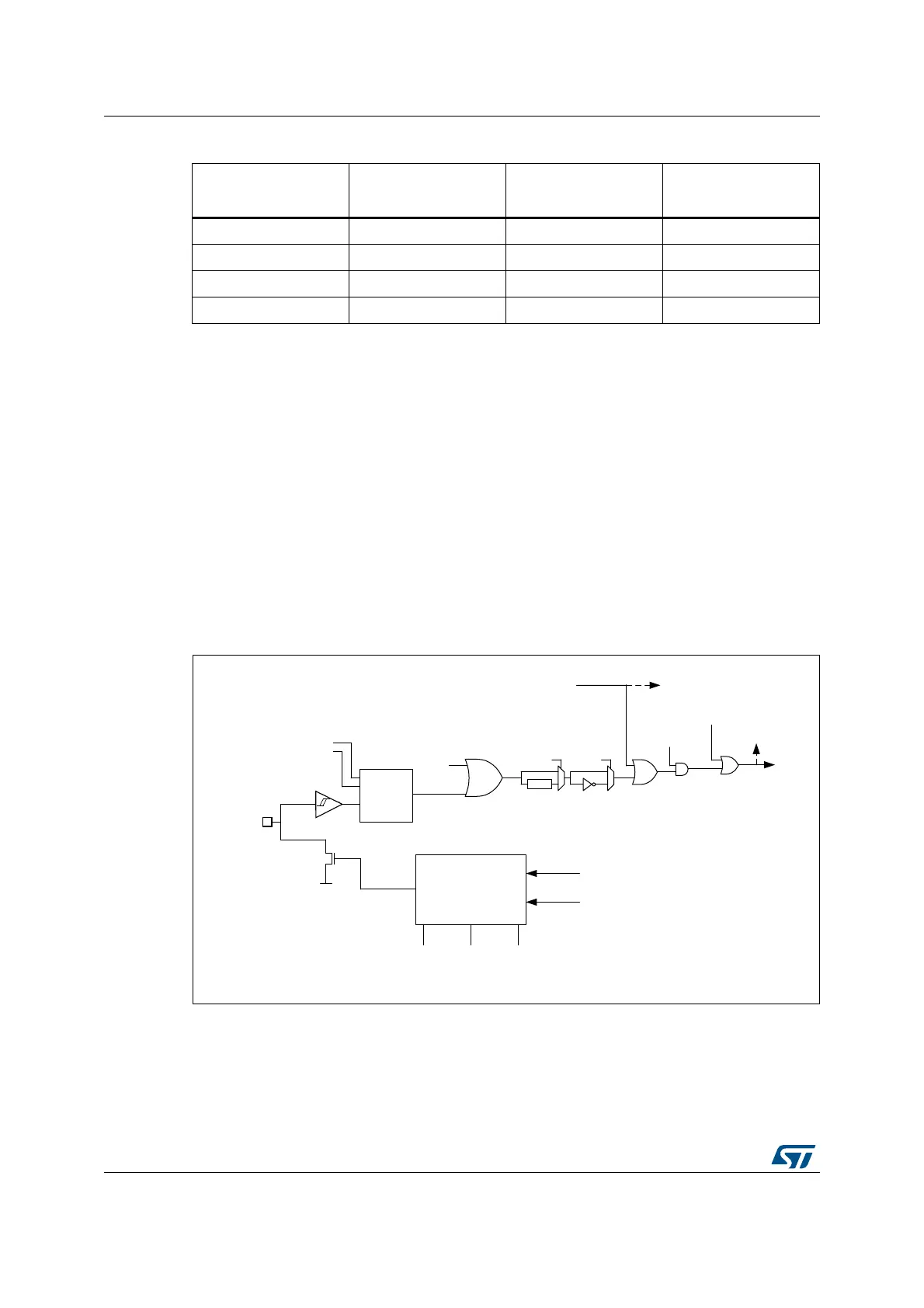

Figure 320. Output redirection (tim_brk2 request not represented)

28.3.20 Clearing the tim_ocxref signal on an external event

The tim_ocxref signal of a given channel can be cleared when a high level is applied on the

tim_ocref_clr_int input (OCxCE enable bit in the corresponding TIMx_CCMRx register set to

1). tim_ocxref remains low until the next update event (UEV) occurs. This function can only

Table 259. Break protection disarming conditions

MOE

BKBID

(BK2BID)

BKDSRM

(BK2DSRM)

Break protection state

0 0 X Armed

0 1 0 Armed

0 1 1 Disarmed

1 X X Armed

MSv62340V1

BKIN inputs from

AF controller

BKF[3:0]

Filter

BKP

BKE

BRK

request

BIF flag

SBIF flag

tim_sys_brk

tim_brk_cmp1..7

AF

controller

mode control logic

MOE BKBID BKBDSRM

tim_brk request

System break request

Bidirectional

Break I/O

TIM_BKIN

Other break inputs

Application break requests

Vss

Bidirectional

AF input

(active low)

AF output

(open drain)

Software break

requests: BG

tim_brk

Loading...

Loading...