Analog-to-digital converters (ADC) RM0440

642/2126 RM0440 Rev 4

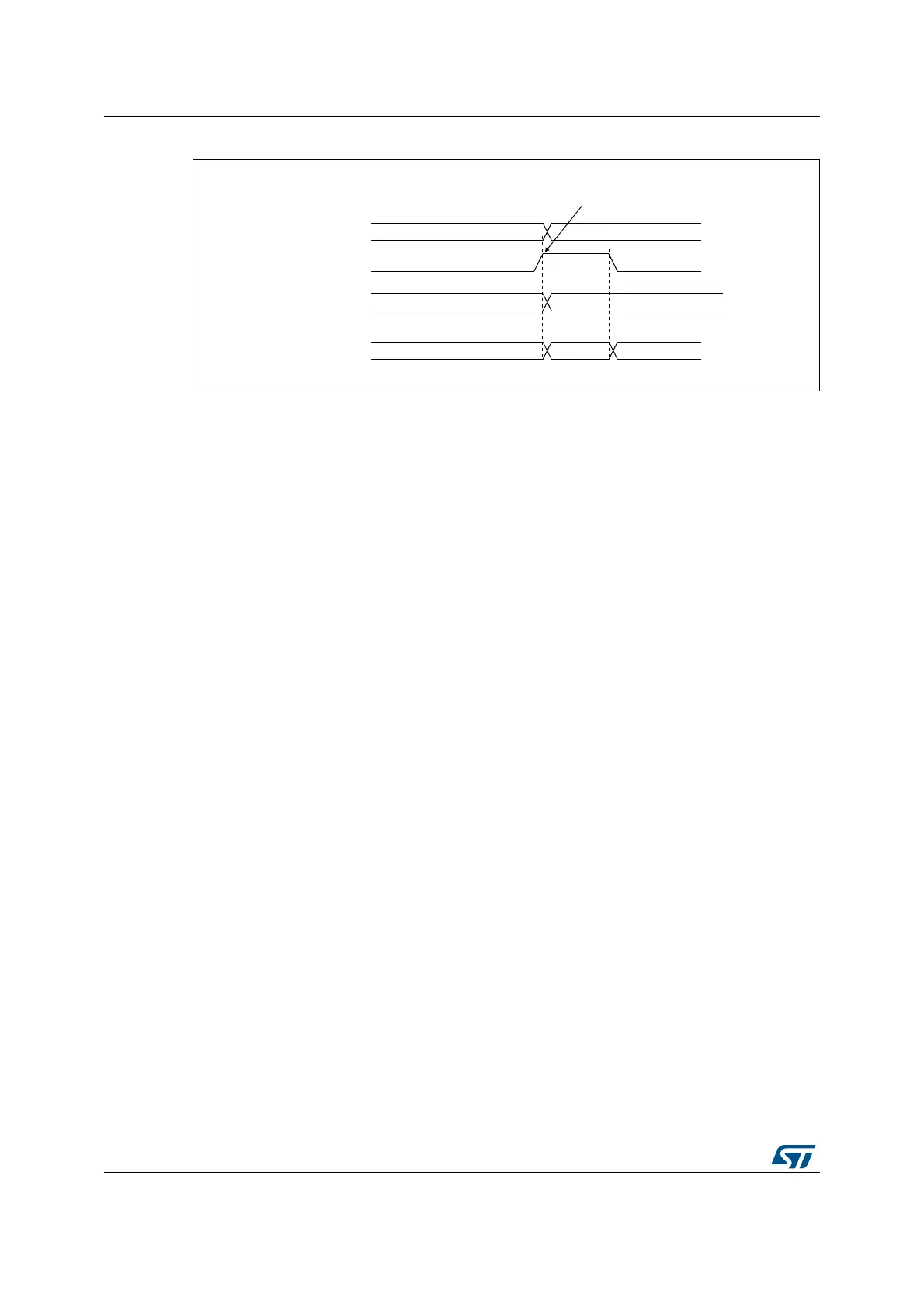

Figure 110. Flushing JSQR queue of context by setting ADDIS=1 (JQM=1)

1. Parameters:

P1: sequence of 1 conversion, hardware trigger 1

P2: sequence of 1 conversion, hardware trigger 1

P3: sequence of 1 conversion, hardware trigger 1

Queue of context: Starting the ADC with an empty queue

The following procedure must be followed to start ADC operation with an empty queue, in

case the first context is not known at the time the ADC is initialized. This procedure is only

applicable when JQM bit is reset:

5. Write a dummy JSQR with JEXTEN[1:0] not equal to 00 (otherwise triggering a

software conversion)

6. Set JADSTART

7. Set JADSTP

8. Wait until JADSTART is reset

9. Set JADSTART.

Disabling the queue

It is possible to disable the queue by setting bit JQDIS=1 into the ADC_CFGR register.

21.4.22 Programmable resolution (RES) - fast conversion mode

It is possible to perform faster conversion by reducing the ADC resolution.

The resolution can be configured to be either 12, 10, 8, or 6 bits by programming the control

bits RES[1:0]. Figure 115, Figure 116, Figure 117 and Figure 118 show the conversion result

format with respect to the resolution as well as to the data alignment.

Lower resolution allows faster conversion time for applications where high-data precision is

not required. It reduces the conversion time spent by the successive approximation steps

according to Table 167.

JSQR queue

ADC state

RDY

P1

P1, P2

REQ-OFF

EMPTY

ADDIS

Queue is flushed and beomes empty

(JSQR is read as 0x0000)

ADC J context

(returned by reading JSQR)

Set

by S/W

Reset

by H/W

MS30547V1

OFF

EMPTY (0x0000)

Loading...

Loading...