System and memory overview RM0440

78/2126 RM0440 Rev 4

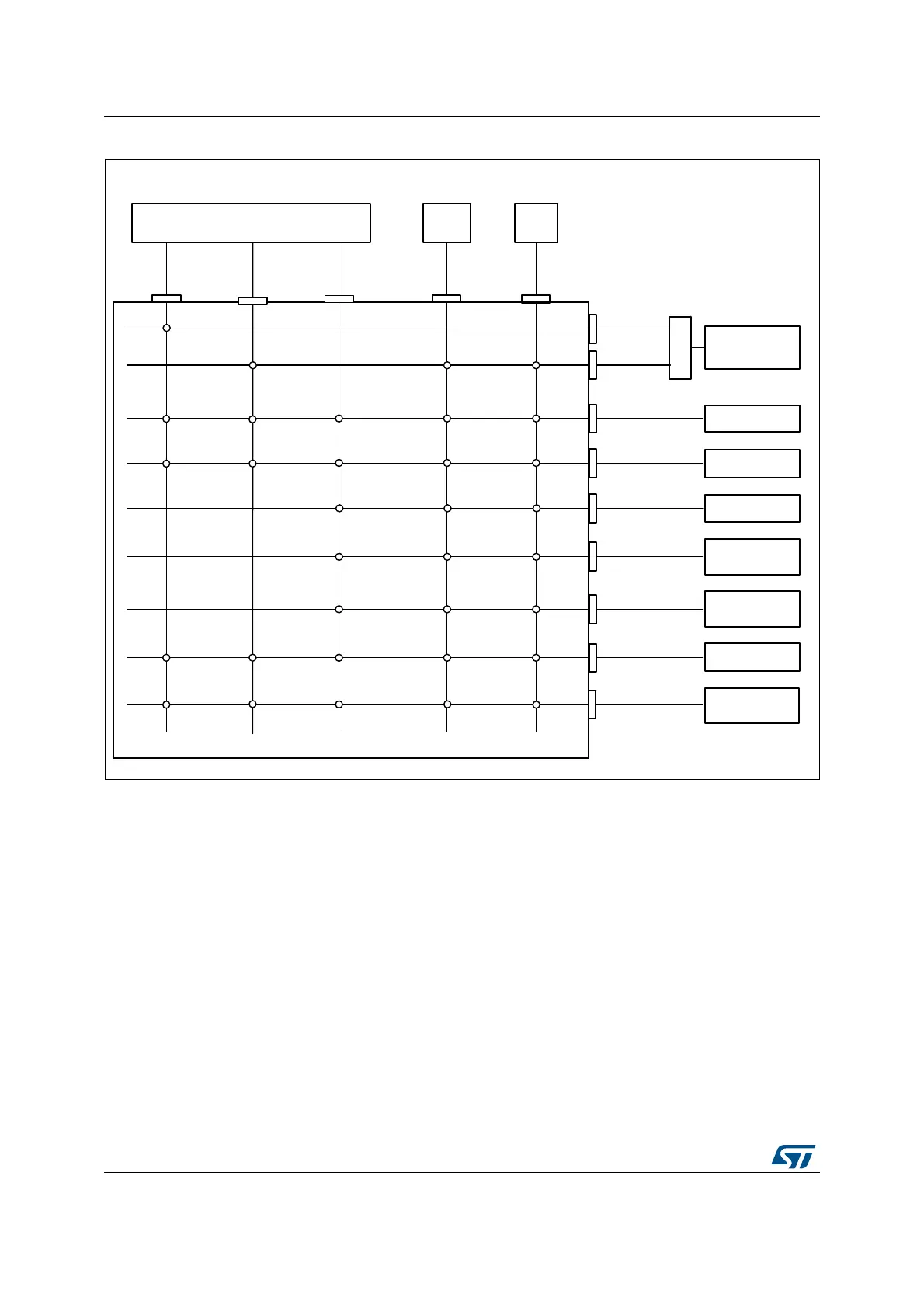

Figure 1. System architecture

2.1.1 I-bus

This bus connects the instruction bus of the Cortex

®

-M4 with FPU core to the BusMatrix.

This bus is used by the core to fetch instructions. The target of this bus is a memory

containing code (either internal Flash memory, internal SRAMs or external memories

through the FSMC or QUADSPI).

2.1.2 D-bus

This bus connects the data bus of the Cortex

®

-M4 with FPU core to the BusMatrix. This bus

is used by the core for literal load and debug access. The target of this bus is a memory

containing code (either internal Flash memory, internal SRAMs or external memories

through the FSMC or QUADSPI).

MSv45850V1

S-bus

D-bus

Cortex

®

-M4

with FPU

DMA1 DMA2

FLASH

512 KB

ACCEL

ICode

DCode

BusMatrix-S

SRAM1

SRAM2

AHB1

peripherals

AHB2

peripherals

FSMC

QUADSPI

I-bus

CCM SRAM

Loading...

Loading...