General-purpose timers (TIM2/TIM3/TIM4/TIM5) RM0440

1290/2126 RM0440 Rev 4

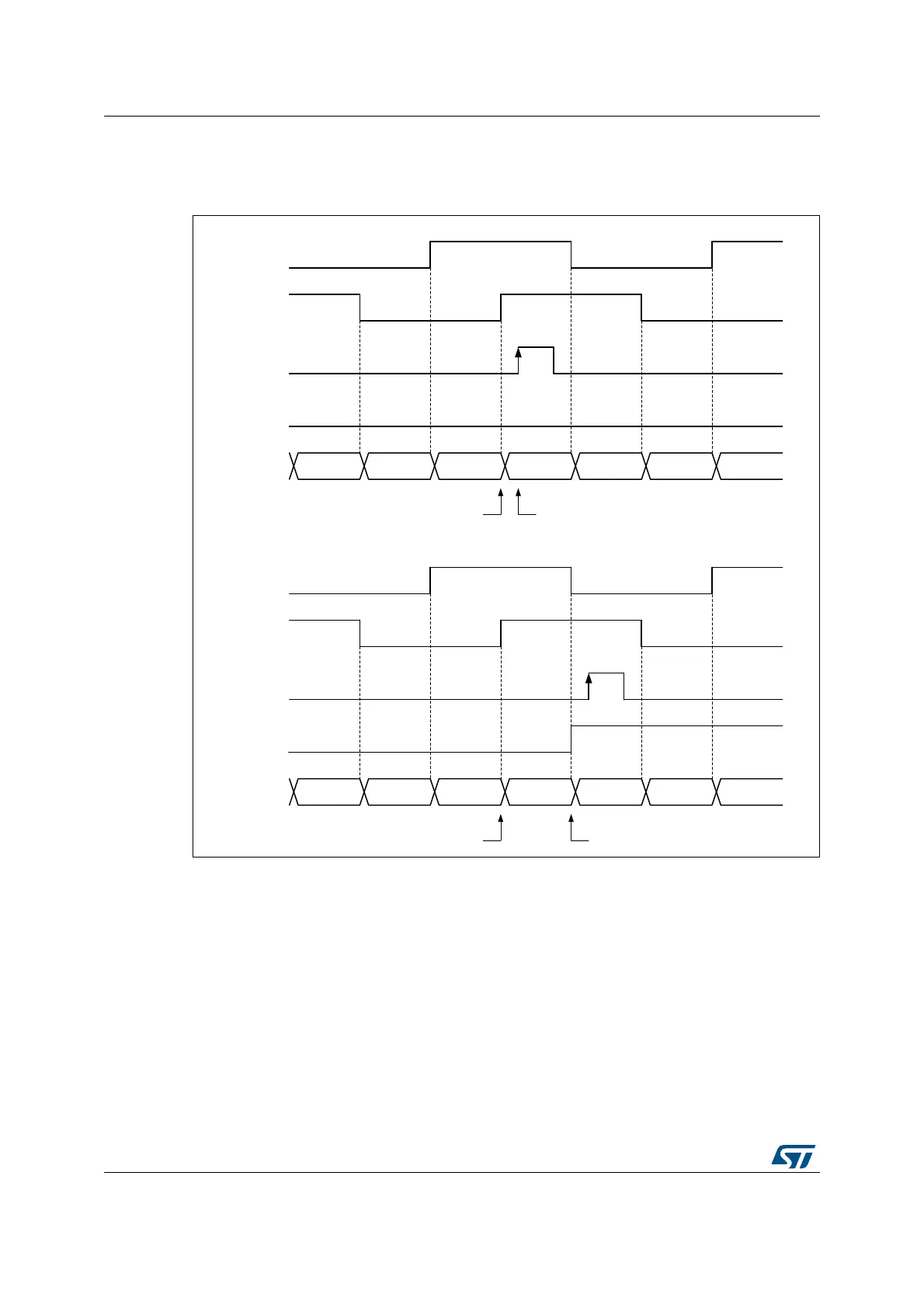

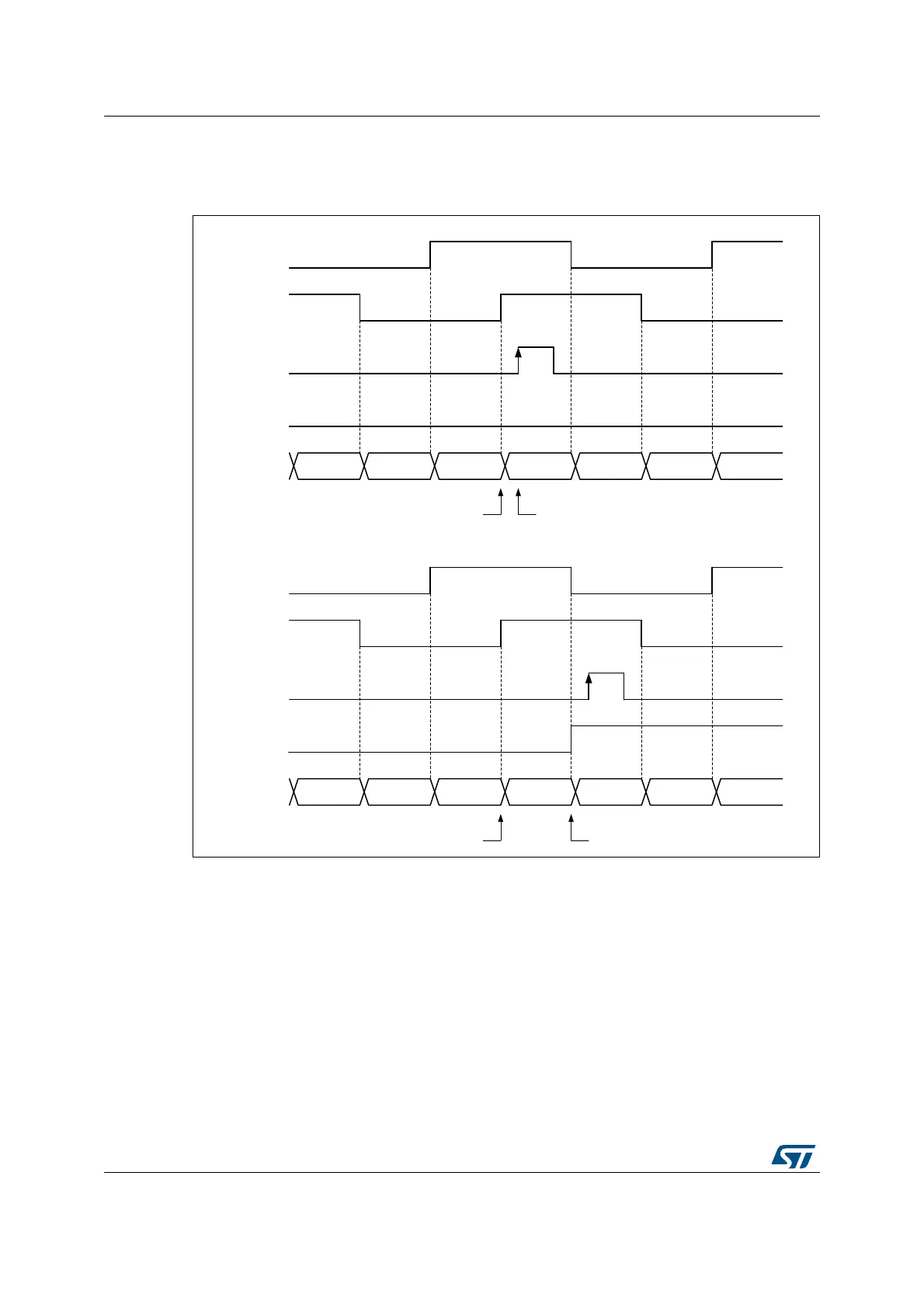

The error assertion is delayed to the transition 0 to 1 when in up-counting. This is cope with

narrow index pulses in gated A and B mode, as shown on Figure 425 below.

Figure 425. Up-counting encoder error detection

MSv45780V1

Channel A

Channel B

IERRF

Index

Channel A

Channel B

IERRF

Index

Counter

5 6 7 0 1

3

2

Counter 5 6 7 0 1

3

2

Error detected Error asserted

Error detected Abort (index detection)

Loading...

Loading...