DMA request multiplexer (DMAMUX) RM0440

426/2126 RM0440 Rev 4

13.3.2 DMAMUX mapping

The mapping of resources to DMAMUX is hardwired.

DMAMUX is used with DMA1 and DMA2:

For category 3 and category 4 devices:

• DMAMUX channels 0 to 7 are connected to DMA1 channels 0 to 7

• DMAMUX channels 8 to 15 are connected to DMA2 channels 0 to 7

For category 2 devices:

• DMAMUX channels 0 to 5 are connected to DMA1 channels 0 to 5

• DMAMUX channels 6 to 11 are connected to DMA2 channels 0 to 5

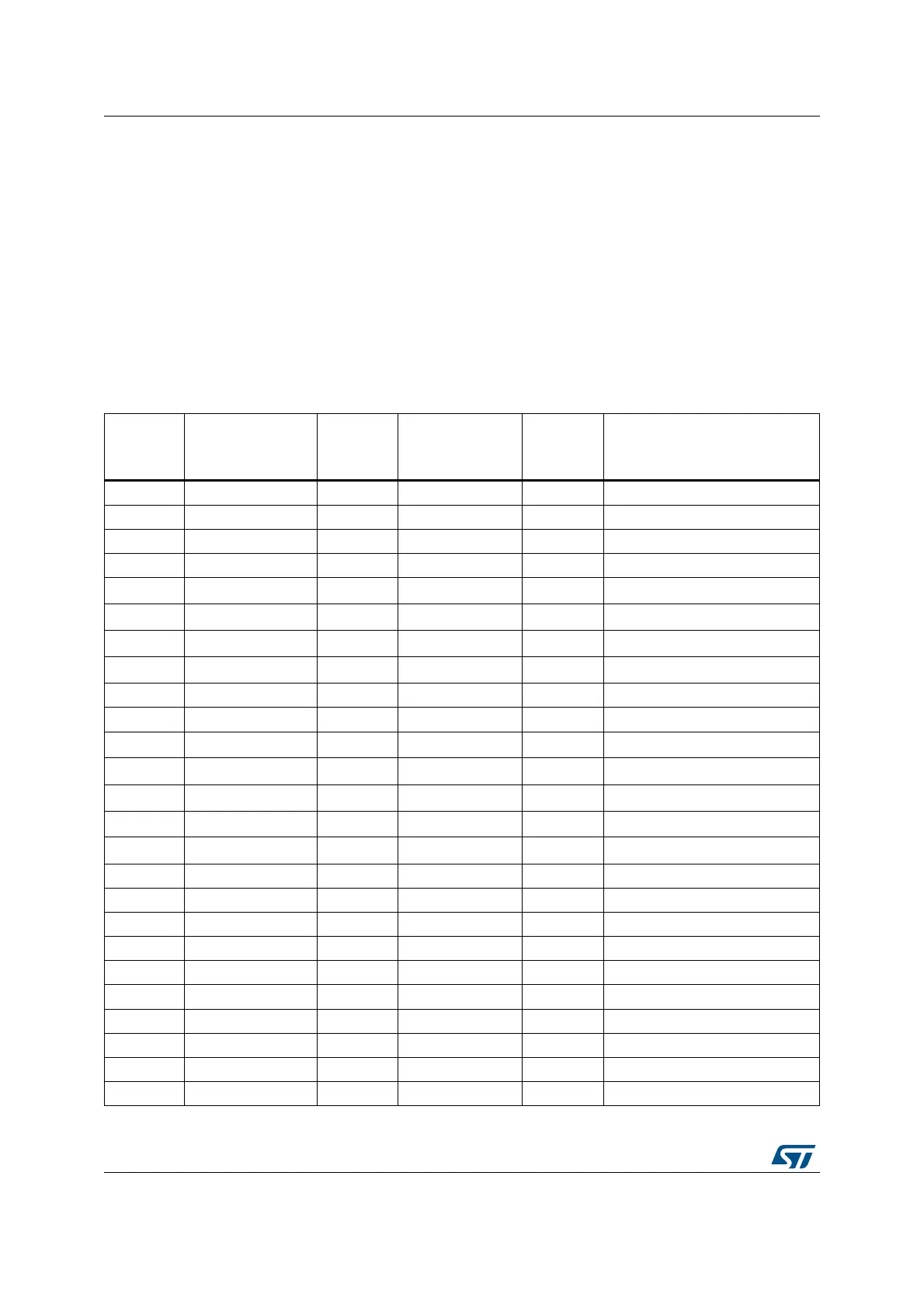

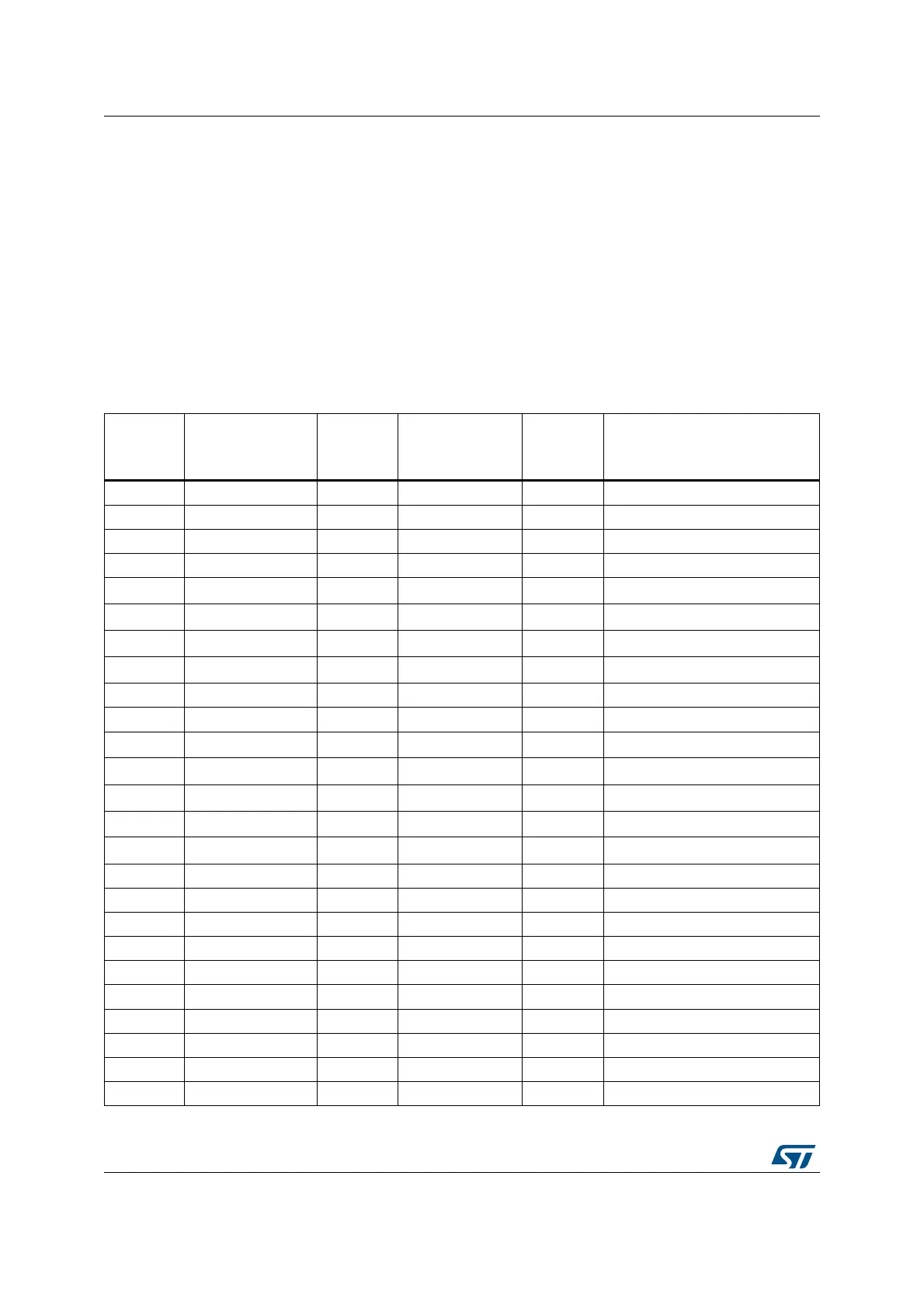

Table 91. DMAMUX: assignment of multiplexer inputs to resources

(1)

DMA

request

MUX input

Resource

DMA

request

MUX input

Resource

DMA

request

MUX input

Resource

1 DMAMUX_Req G0 44 TIM1_CH3 87 TIM20_CH2

2 DMAMUX_Req G1 45 TIM1_CH4 88 TIM20_CH3

3 DMAMUX_Req G2 46 TIM1_UP 89 TIM20_CH4

4 DMAMUX_Req G3 47 TIM1_TRIG 90 TIM20_UP

5 ADC1 48 TIM1_COM 91 AES_IN

6 DAC1_CH1 49 TIM8_CH1 92 AES_OUT

7 DAC1_CH2 50 TIM8_CH2 93 TIM20_TRIG

8 TIM6_UP 51 TIM8_CH3 94 TIM20_COM

9 TIM7_UP 52 TIM8_CH4 95 HRTIM_MASTER (hrtim_dma1)

10 SPI1_RX 53 TIM8_UP 96 HRTIM_TIMA (hrtim_dma2)

11 SPI1_TX 54 TIM8_TRIG 97 HRTIM_TIMB (hrtim_dma3)

12 SPI2_RX 55 TIM8_COM 98 HRTIM_TIMC (hrtim_dma4)

13 SPI2_TX 56 TIM2_CH1 99 HRTIM_TIMD (hrtim_dma5)

14 SPI3_RX 57 TIM2_CH2 100 HRTIM_TIME (hrtim_dma6

15 SPI3_TX 58 TIM2_CH3 101 HRTIM_TIMF (hrtim_dma7)

16 I2C1_RX 59 TIM2_CH4 102 DAC3_CH1

17 I2C1_TX 60 TIM2_UP 103 DAC3_CH2

18 I2C2_RX 61 TIM3_CH1 104 DAC4_CH1

19 I2C2_TX 62 TIM3_CH2 105 DAC4_CH2

20 I2C3_RX 63 TIM3_CH3 106 SPI4_RX

21 I2C3_TX 64 TIM3_CH4 107 SPI4_TX

22 I2C4_RX 65 TIM3_UP 108 SAI1_A

23 I2C4_TX 66 TIM3_TRIG 109 SAI1_B

24 USART1_RX 67 TIM4_CH1 110 FMAC_Read

25 USART1_TX 68 TIM4_CH2 111 FMAC_Write

Loading...

Loading...