RM0440 Rev 4 1377/2126

RM0440 General-purpose timers (TIM15/TIM16/TIM17)

1445

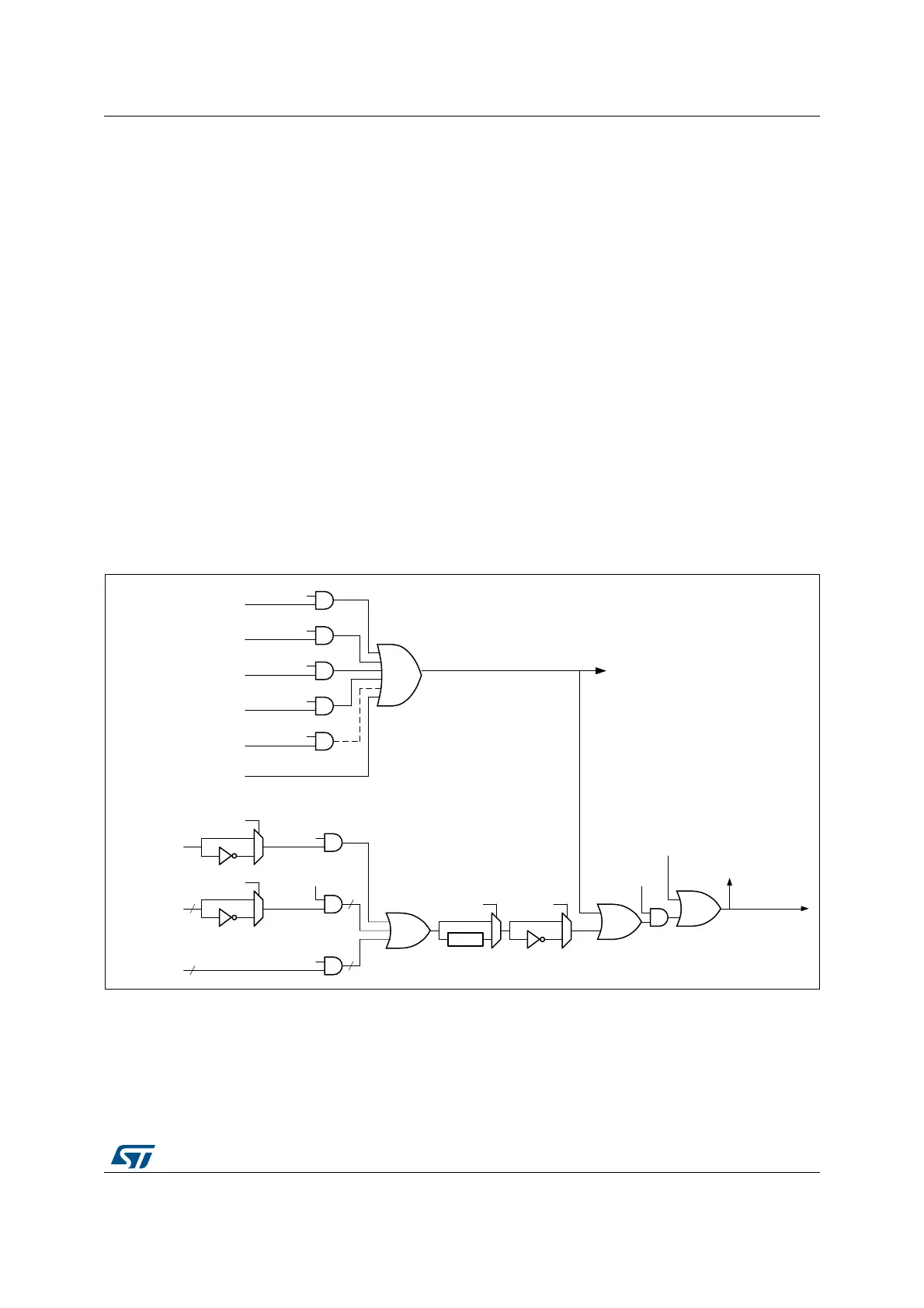

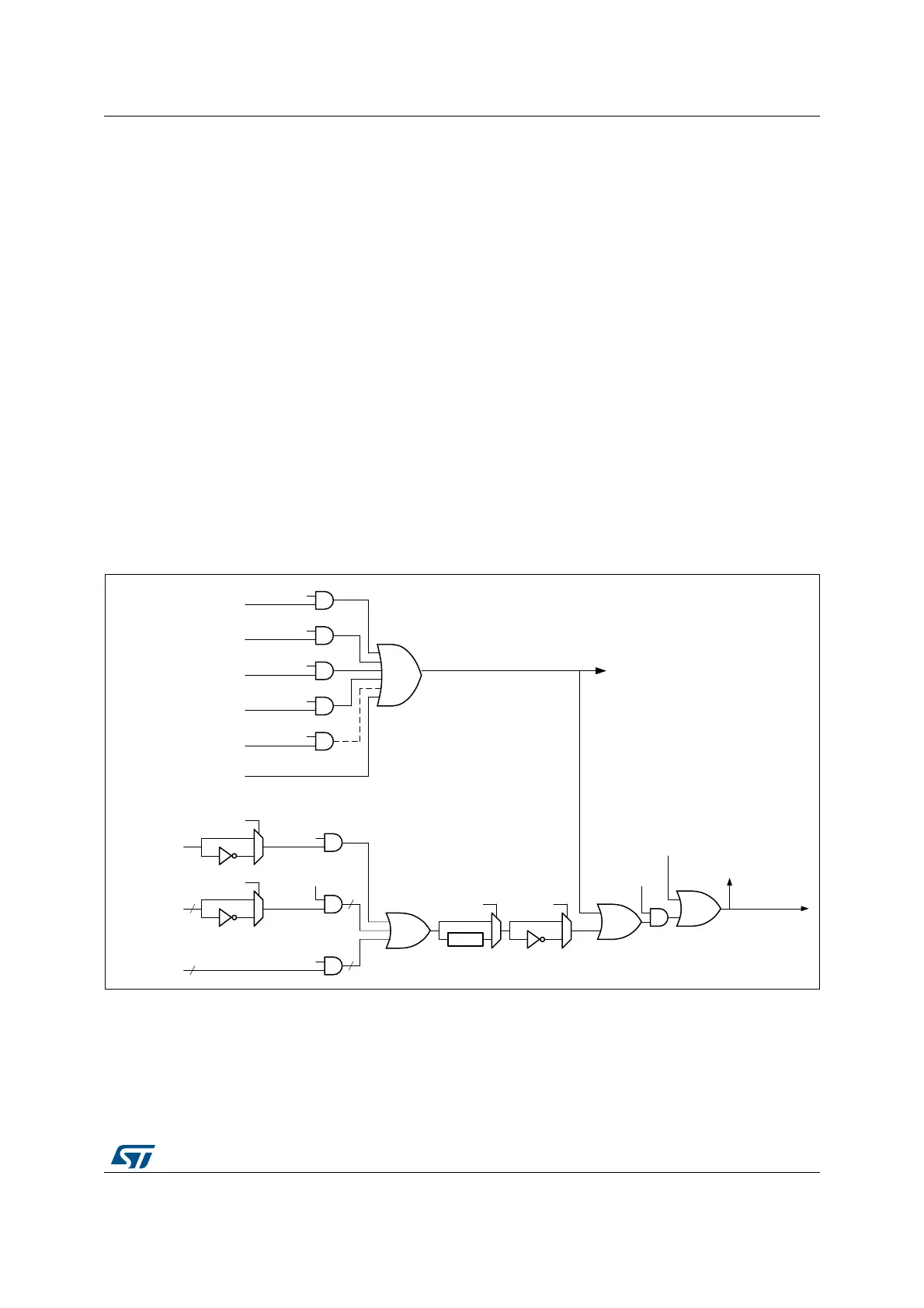

The break is generated by the tim_brk inputs which has:

• Programmable polarity (BKP bit in the TIMx_BDTR register)

• Programmable enable bit (BKE bit in the TIMx_BDTR register)

• Programmable filter (BKF[3:0] bits in the TIMx_BDTR register) to avoid spurious

events.

The break can be generated from multiple sources which can be individually enabled and

with programmable edge sensitivity, using the TIMx_AF1 register.

The sources for break (tim_brk) channel are:

• External sources connected to one of the TIM_BKIN pin (as per selection done in the

AFIO controller), with polarity selection and optional digital filtering

• Internal sources:

– coming from a tim_brk_cmpx input (refer to Section 30.4.2: TIM15/TIM16/TIM17

pins and internal signals for product specific implementation)

– coming from a system break request on the tim_sys_brk inputs (refer to

Section 30.4.2: TIM15/TIM16/TIM17 pins and internal signals for product specific

implementation)

Break events can also be generated by software using BG bit in the TIMx_EGR register. All

sources are ORed before entering the timer tim_brk inputs, as per Figure 469 below.

Figure 469. Break circuitry overview

Caution: An asynchronous (clockless) operation is only guaranteed when the programmable filter is

disabled. If it is enabled, a fail safe clock mode (for example, using the internal PLL and/or

the CSS) must be used to guarantee that break events are handled.

MSv62368V1

Enable

Enable

Enable

Enable

tim_sys_brk3

tim_sys_brk2

tim_sys_brk1

tim_sys_brk0

CSS

SBIF flag

tim_sys_brk

BKCMP5E..BKCMP7E

TIMx_BKIN

from AF

controller

BKINE

BKINP

Software break

requests: BG

BKE

Application break requests

tim_brk

BIF flag

tim_brk_cmp5..7

3

tim_brk_cmp1..4

BKCMP4E

BKCMP1P..BKCMP4P

4

4

3

BKF[3:0] BKP

BKCMP1E

...

Filter

Enable

tim_sys_brkx

Loading...

Loading...