Analog-to-digital converters (ADC) RM0440

618/2126 RM0440 Rev 4

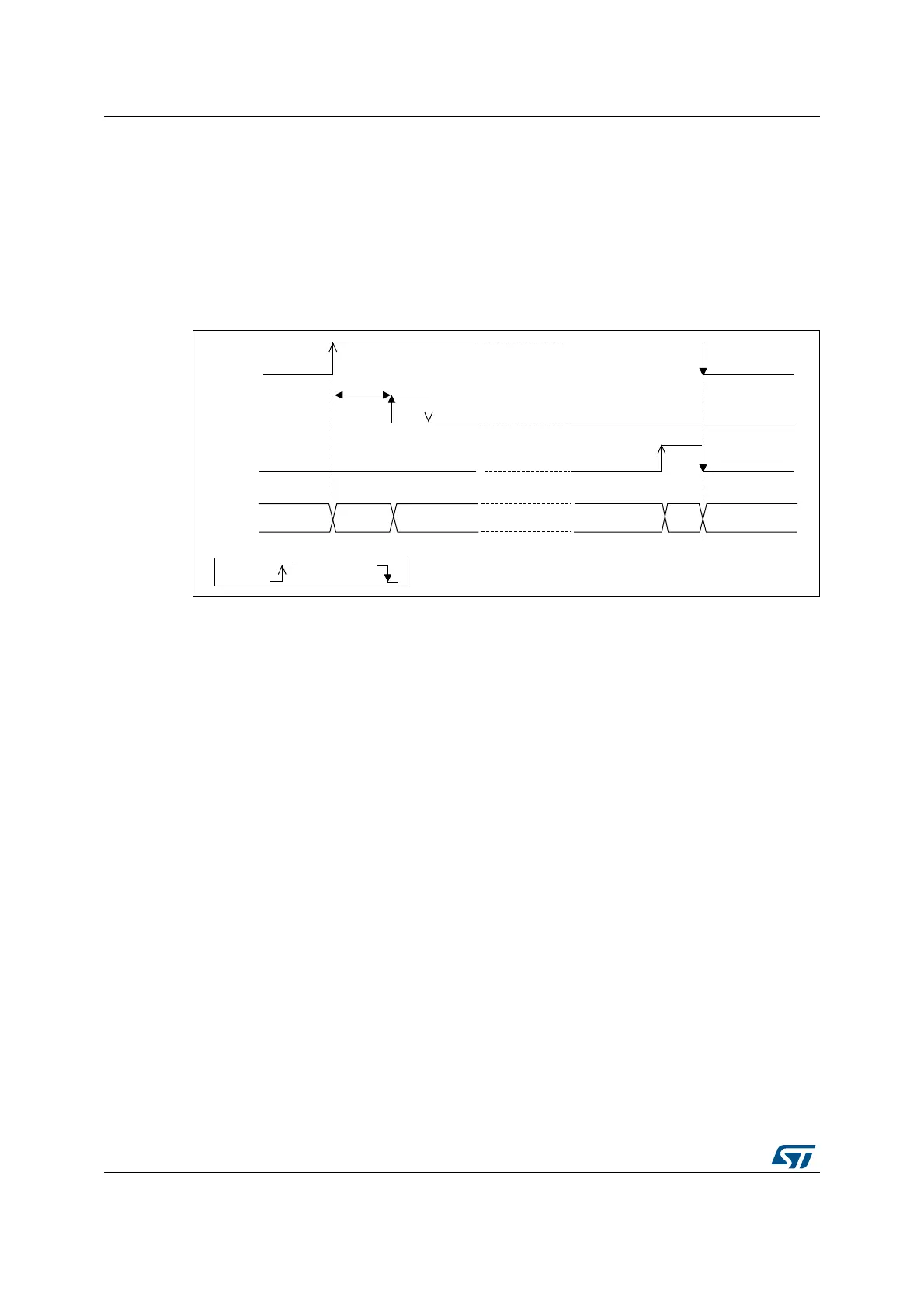

Software procedure to disable the ADC

1. Check that both ADSTART=0 and JADSTART=0 to ensure that no conversion is

ongoing. If required, stop any regular and injected conversion ongoing by setting

ADSTP=1 and JADSTP=1 and then wait until ADSTP=0 and JADSTP=0.

2. Set ADDIS=1.

3. If required by the application, wait until ADEN=0, until the analog ADC is effectively

disabled (ADDIS will automatically be reset once ADEN=0).

Figure 92. Enabling / disabling the ADC

21.4.10 Constraints when writing the ADC control bits

The software is allowed to write the RCC control bits to configure and enable the ADC clock

(refer to RCC Section), the DIFSEL[i] control bits in the ADC_DIFSEL register and the

control bits ADCAL and ADEN in the ADC_CR register, only if the ADC is disabled (ADEN

must be equal to 0).

The software is then allowed to write the control bits ADSTART, JADSTART and ADDIS of

the ADC_CR register only if the ADC is enabled and there is no pending request to disable

the ADC (ADEN must be equal to 1 and ADDIS to 0).

For all the other control bits of the ADC_CFGR, ADC_SMPRx, ADC_TRy, ADC_SQRy,

ADC_JDRy, ADC_OFRy, ADC_OFCHRy and ADC_IER registers:

• For control bits related to configuration of regular conversions, the software is allowed

to write them only if the ADC is enabled (ADEN=1) and if there is no regular conversion

ongoing (ADSTART must be equal to 0).

• For control bits related to configuration of injected conversions, the software is allowed

to write them only if the ADC is enabled (ADEN=1) and if there is no injected

conversion ongoing (JADSTART must be equal to 0).

• ADC_TRy registers can be modified when an analog-to-digital conversion is ongoing

(refer to Section 21.4.28: Analog window watchdog (AWD1EN, JAWD1EN, AWD1SGL,

AWD1CH, AWD2CH, AWD3CH, AWD_HTx, AWD_LTx, AWDx)for details).

The software is allowed to write the ADSTP or JADSTP control bits of the ADC_CR register

only if the ADC is enabled, possibly converting, and if there is no pending request to disable

the ADC (ADSTART or JADSTART must be equal to 1 and ADDIS to 0).

MSv30264V2

t

STAB

ADEN

ADRDY

ADDIS

ADC

Converting CH

OFF

by H/W

by S/W

REQ

-OF

state

OFF Startup RDY RDY

Loading...

Loading...