RM0440 Rev 4 405/2126

RM0440 Direct memory access controller (DMA)

423

may stop the CPU access to the system bus for a number of bus cycles, when CPU and

DMA target the same destination (memory or peripheral).

According to its configuration through the AHB slave interface, the DMA controller arbitrates

between the DMA channels and their associated received requests. The DMA controller

also schedules the DMA data transfers over the single AHB port master.

The DMA controller generates an interrupt per channel to the interrupt controller.

12.4.2 DMA pins and internal signals

12.4.3 DMA transfers

The software configures the DMA controller at channel level, in order to perform a block

transfer, composed of a sequence of AHB bus transfers.

A DMA block transfer may be requested from a peripheral, or triggered by the software in

case of memory-to-memory transfer.

After an event, the following steps of a single DMA transfer occur:

1. The peripheral sends a single DMA request signal to the DMA controller.

2. The DMA controller serves the request, depending on the priority of the channel

associated to this peripheral request.

3. As soon as the DMA controller grants the peripheral, an acknowledge is sent to the

peripheral by the DMA controller.

4. The peripheral releases its request as soon as it gets the acknowledge from the DMA

controller.

5. Once the request is de-asserted by the peripheral, the DMA controller releases the

acknowledge.

The peripheral may order a further single request and initiate another single DMA transfer.

The request/acknowledge protocol is used when a peripheral is either the source or the

destination of the transfer. For example, in case of memory-to-peripheral transfer, the

peripheral initiates the transfer by driving its single request signal to the DMA controller. The

DMA controller reads then a single data in the memory and writes this data to the peripheral.

For a given channel x, a DMA block transfer consists of a repeated sequence of:

• a single DMA transfer, encapsulating two AHB transfers of a single data, over the DMA

AHB bus master:

– a single data read (byte, half-word or word) from the peripheral data register or a

location in the memory, addressed through an internal current peripheral/memory

address register.

The start address used for the first single transfer is the base address of the

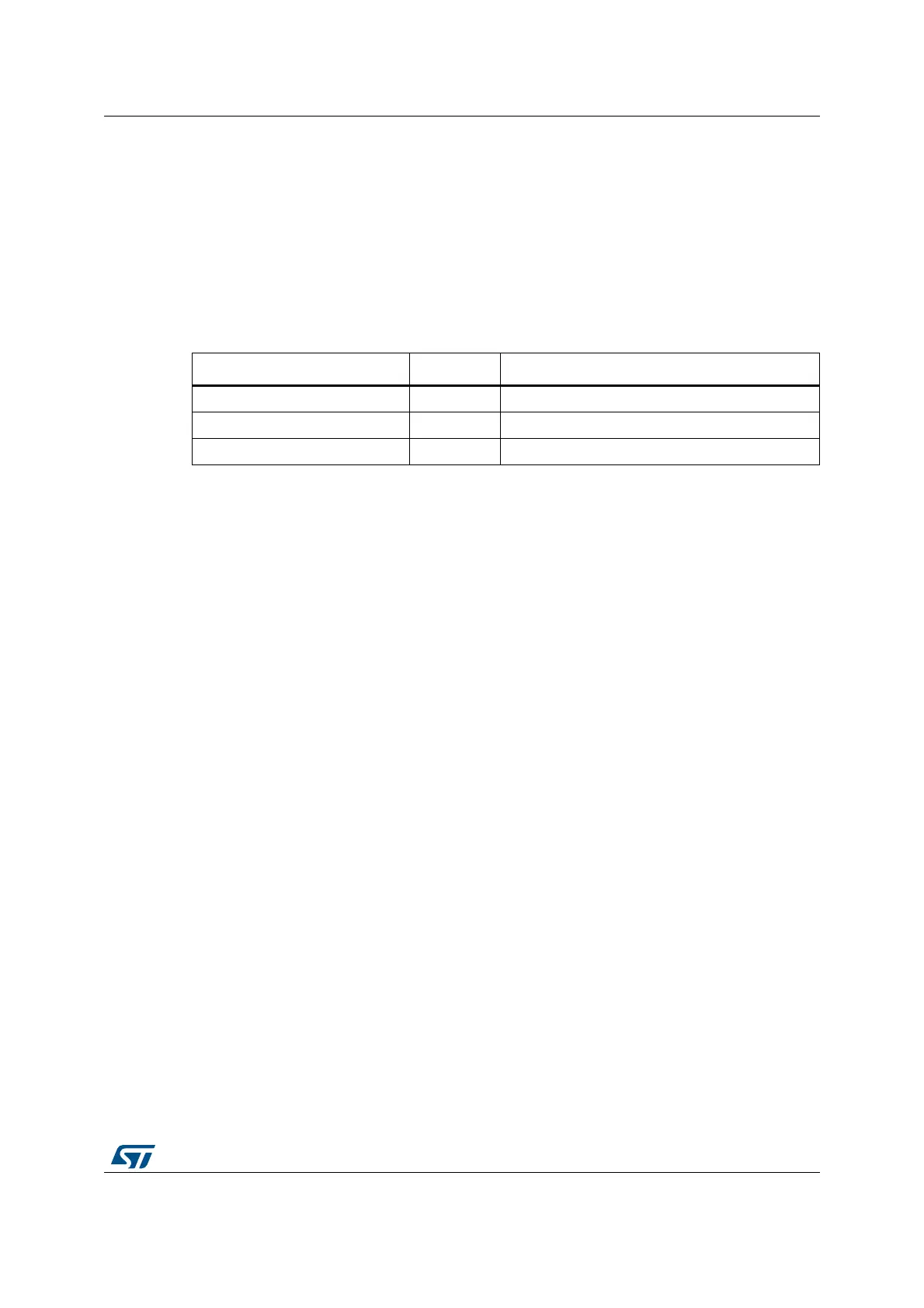

Table 86. DMA internal input/output signals

Signal name Signal type Description

dma_req[x] Input DMA channel x request

dma_ack[x] Output DMA channel x acknowledge

dma_it[x] Output DMA channel x interrupt

Loading...

Loading...